#### **Xilinx Tool Flow**

© 2005 Xilinx, Inc. All Rights Reserved

## Objectives

#### After completing this module, you will be able to:

- List the steps of the Xilinx design process

- Implement and simulate an FPGA design by using default software options

## Outline

- Overview

- · ISE

- . Summary

- · Lab 1: Xilinx Tool Flow Demo

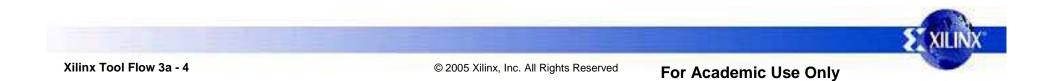

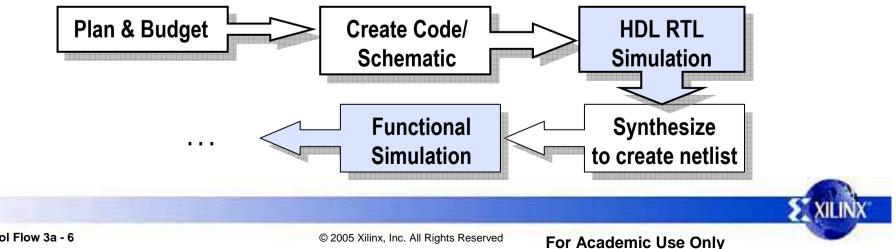

## **Xilinx Design Flow**

# **Design Entry**

- Plan and budget .

- Two design-entry methods: HDL or schematic •

- Architecture Wizard, CORE Generator<sup>™</sup> system, and StateCAD tools are available to assist in design entry

- Whichever method you use, you will need a tool to generate an EDIF or NGC • netlist to bring into the Xilinx implementation tools

- Popular synthesis tools include: Synplify, Precision, FPGA Compiler II, and XST

- Simulate the design to ensure that it works as expected!

## **Xilinx Implementation**

- Once you generate a netlist, you can implement the design

- There are several outputs of implementation

- Reports

- Timing simulation netlists

- Floorplan files

- FPGA Editor files

- and more!

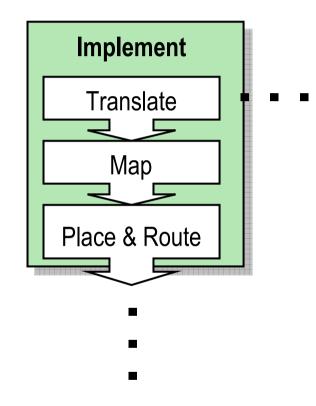

# What is Implementation?

• More than just *Place & Route*

- Implementation includes many phases

- Translate: Merge multiple design files into a single netlist

- Map: Group logical symbols from the netlist (gates) into physical components (slices and IOBs)

- Place & Route: Place components onto the chip, connect the components, and extract timing data into reports

- Each phase generates files that allow you to use other Xilinx tools

- Floorplanner, FPGA Editor, XPower

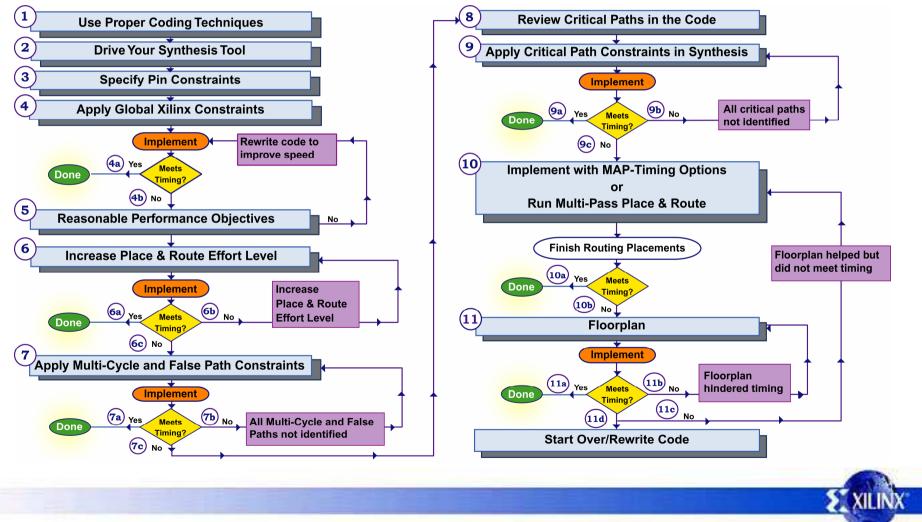

## **Timing Closure**

#### Download

- Once a design is implemented, you must create a file that the FPGA can understand

- This file is called a bitstream: a BIT file (.bit extension)

- The BIT file can be downloaded directly into the FPGA, or the BIT file can be converted into a PROM file, which stores the programming information

•

© 2005 Xilinx, Inc. All Rights Reserved

For Academic Use Only

## Outline

Overview

- Summary

- · Lab 1: Xilinx Tool Flow Demo

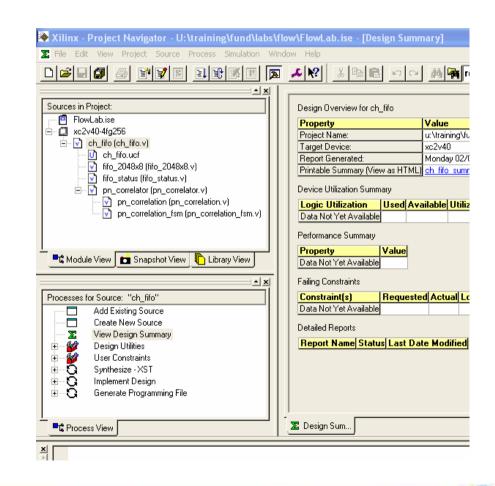

# **ISE Project Navigator**

- Built around the Xilinx design flow

- Access to synthesis and schematic tools

- Including third-party synthesis tools

- Implement your design with a simple double-click

- Fine-tune with easy-to-access software options

# Implementing a Design

Sources in Project: Implement a design: • 🖻 FlowLab vo2v40-46a256 Select the **top-level source** \_ 🗄 – 📝 – ch\_fifo (ch\_fifo.v) file in the Sources in Project fifo\_2048x8 (fifo\_2048x8.v) window fifo\_status (fifo\_status.v) pn\_correlator (pn\_correlator.v) HDL, schematic, or EDIF, pn\_correlation (pn\_correlation.v) pn\_correlation\_fsm (pn\_correlation\_fsm.v) **V**1 depending on your design flow Contract Module View 💼 Snapshot View Library View Double-click Implement \_ Processes for Source: "ch fifo" **Design** in the Processes for Add Existing Source Create New Source Source window Σ View Design Summary 6 Design Utilities ۶đ User Constraints Sunthesize - XST Implement Design Generate Programming File Process View

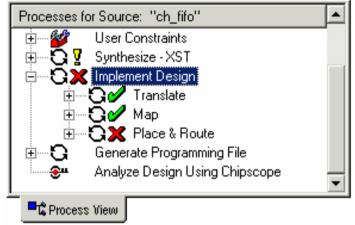

#### **Implementation Status**

- The ISE<sup>™</sup> software will run all of the necessary steps to implement the design

- Synthesize HDL code

- Translate

- Мар

- Place & Route

- Progress and status are indicated by icons

- Yellow exclamation point (!) indicates warnings

- Yellow question mark (?) indicates a file that is out of date

- Red X indicates errors

#### **Software Update Center**

- Automatically checks for Service • Packs on the Web

- Alerts you when an update is • available

- Supports Windows platforms only •

| Update from the Web                                                   | ×       |

|-----------------------------------------------------------------------|---------|

| Please wait, checking for available updates at<br>support.xilinx.com. |         |

| Checking for available service packs.                                 |         |

| Product: ISE Foundation                                               |         |

| Current Version: 6.3i<br>Update Version:                              | Details |

| OK Cancel                                                             | Help    |

|                                                                       |         |

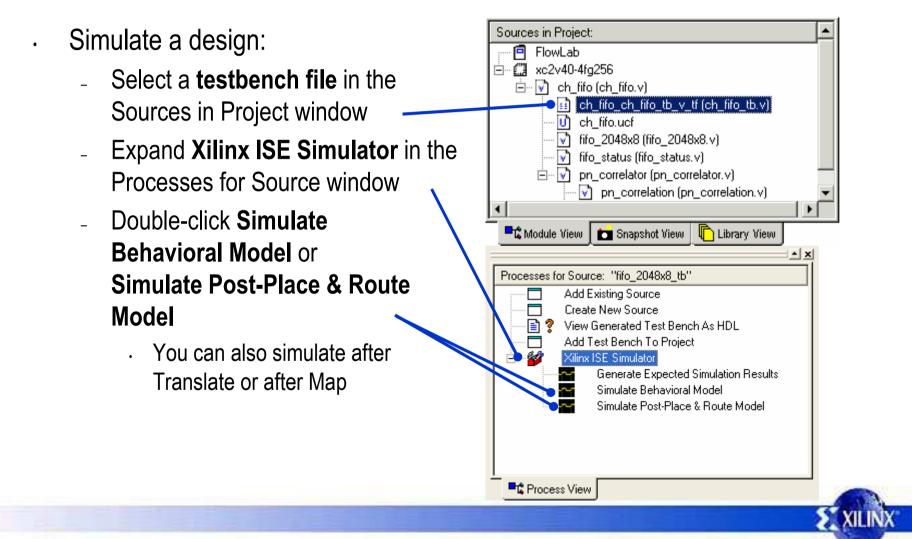

# Simulating a Design

© 2005 Xilinx, Inc. All Rights Reserved

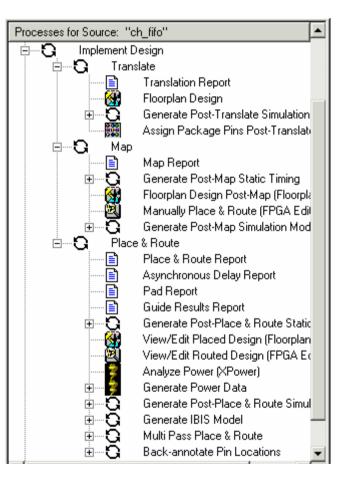

#### Subprocesses

- Expand each process to view subtools and subprocesses

- Translate

- · Floorplan

- Assign package pins

- Map

- · Analyze timing

- Place & Route

- Analyze timing

- · Floorplan

- · FPGA Editor

- · Analyze power

- · Create simulation model

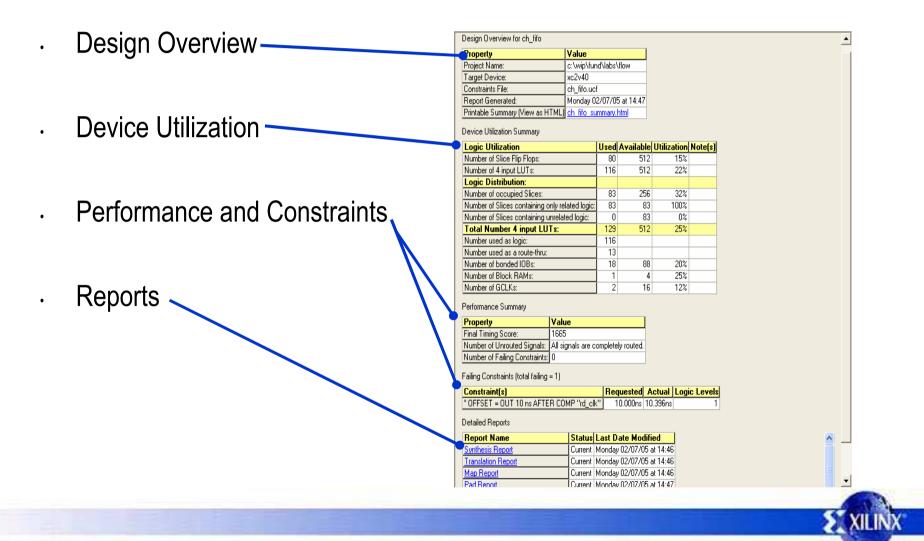

## **Project Summary**

© 2005 Xilinx, Inc. All Rights Reserved

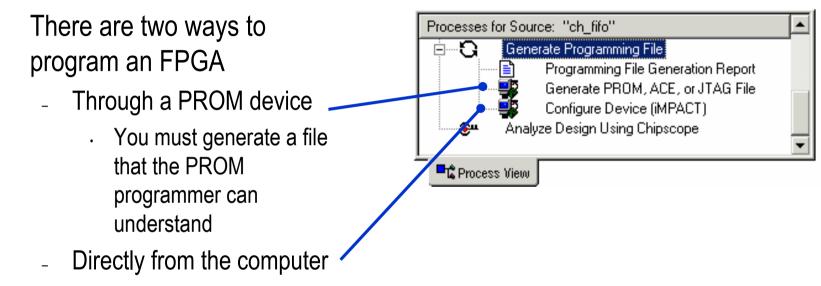

## **Programming the FPGA**

• Use the iMPACT configuration tool

## **Outline**

- Overview •

- ISE •

- **Summary** •

- Lab 1: Xilinx Tool Flow Demo •

### **Review Questions**

- What are the phases of the Xilinx design flow? •

- What are the components of implementation, and what happens • at each step?

- What are two methods of programming an FPGA? •

#### Answers

- What are the phases of the Xilinx design flow?

- Plan and budget, create code or schematic, RTL simulation, synthesize, functional simulation, implement, timing closure, timing simulation, and BIT file creation

- What are the components of implementation, and what happens at each step?

- Translate: merges multiple design files into one netlist

- Map: groups logical symbols into physical components

- Place & Route: places components onto the chip and connects them

- What are two methods of programming an FPGA?

- PROM

- Xilinx iMPACT configuration tool

•

•

## Summary

- Implementation means more than Place & Route

- Xilinx provides a simple *pushbutton* tool to guide you through the Xilinx design process

## Where Can I Learn More?

- Complete design flow tutorials

- www.xilinx.com  $\rightarrow$  Documentation  $\rightarrow$  Tutorials

- On implementation: Development System Reference Guide

- www.xilinx.com  $\rightarrow$  Documentation  $\rightarrow$  Software Manuals \_

- Documentation may also be installed on your local computer

- On simulation: ISIM Online Help •

- **Configuration Problem Solver** •

- www.xilinx.com  $\rightarrow$  Support  $\rightarrow$  Problem Solvers  $\rightarrow$  Configuration Problem \_ Solver

•

## Outline

- · Overview

- · ISE

- Summary

- Lab 1: Xilinx Tool Flow Demo

#### **Software Demo**

- Follow along with the instructor:

- Launch the ISE<sup>™</sup> Project Navigator \_

- Create a project \_

- Add design files to the project \_

- Simulate the design \_

- Implement the design \_

- After the design has been implemented, you will examine some reports in the next module

•