# System Organization

# Lab Manual, Chapter Three

A good assembly language programmer needs to know a little more than an assembly language instruction set. An in-depth understanding of the underlying computer architecture is also necessary. Unless you know the internal operation of the instructions and how these internal operations interact, you cannot write the fastest possible assembly language code. Likewise, without knowing how a machine encodes instructions, you will not be able to predict if one instruction sequence is shorter or longer than another.

In this laboratory you will learn how to use a rudimentary *debugger* to create, test, and execute short *machine language programs*. You will also explore *cycle counting* and *byte-counting* program optimization methods. These are skills which are important when working with complex assembly language programs.

#### 3.1 Debuggers and SIM886

A debugger is a program which lets you display and modify different memory locations, execute instructions, display machine registers, and perform other common operations necessary to test and correct machine language programs. The correct use of a debugger will dramatically reduce the time you spend testing and correcting assembly language programs. In this laboratory you will use a very simple machine language debugger for the x86 processors. This will provide a gentle introduction to the CodeView debugger which Chapter Four describes.

Before describing the debugger itself, a discussion of the x86 simulator is necessary. Since the x86 processors are hypothetical, there isn't any hardware on which you can run an x86 program. The x86 simulator (SIM886) is a piece of software which simulates an x86 processor. This program fetches x86 opcodes from memory (the 80x86's) and then executes a sequence of instructions which emulates the behavior of those instructions.

The SIM886 program uses integer variables to hold the values of the 886 registers and memory locations. For all intents and purposes, you could not tell the difference between the SIM886 program and an actual 886 processor (if one existed). This simulation technique is not limited to hypothetical processors, by the way. SoftPC and other programs use this very technique to emulate an 80x86 processor on Macintosh, NeXT, and other computer systems.

The SIM886 program can control the LED and switch circuitry you built for the lab exercises in Chapter Two. When you run SIM886, it defaults to LPT1:. If you use the circuitry and you install it in a parallel port other than LPT1:, you should specify the port name as a command line argument to the SIM886 program:

c:> sim886 lpt1: c:> sim886 lpt2: c:> sim886 lpt3:

#### 3.1.1 Displaying and Entering Memory Values

The SIM886 program simulates the 64K address space of the 886 processor using a 64K array in the 80x86 memory space. Whatever would normally appear at memory location zero on the 886 processor winds up at index zero in that array. Like any decent debugger, the SIM886 program lets you display and enter memory values. When you first run the SIM886 program, it initializes all bytes in the 886 memory space so that they contain 0E0h (which turns out to be the opcode of the 886 HALT instruction). You can verify this by using the SIM886 "D" (for Dump or Display). This command takes the form:

D address

This command displays up to 16 bytes of data starting at the specified address. For example, the command "D 1000" displays 16 bytes starting at address  $1000h^1$  as follows:

....

. . .

<sup>1.</sup> All constant values in the debugger are hexadecimal values. You do not need to (in fact, you cannot) place the "H" suffix after the value.

The first E0 above is the value for location 1000h, the second E0 is the value contained in location 1001h, ..., the last E0 displayed above is for location 100Fh. Note that there are extra spaces between the values for 1003h/1004h, 1007h/ 1008h, and 100Bh/100Ch. This makes locating a specific value on the line a little easier.

The **D**ump command is very useful for displaying the values of variables, arrays, or even machine code (binary representations for instructions). However, you must always keep one important point in mind– the **D**ump command displays values across the line from a low address to a high address. This seems reasonable enough. But note that word values, which the 886 processors stores in two consecutive bytes with the low-order byte at the lowest address and the high-order byte at the highest address, will appear backwards on the dump display. If the word at address 1000h contains 1234h and you use the **D**ump command, you'll see something like the following:

You must remember to mentally swap the values around when reading them from the screen. A very common mistake beginners make is to forget to swap the bytes displayed by the debugger.

The **D**ump command lets you view the contents of memory, the **E**nter command lets you change the contents of one or more memory locations. The format for the **E**nter command is

E address

This instructs the SIM886 program to begin accepting input values from the keyboard. Immediately after you enter the command "E 1000" SIM886 responds with

1000(E0): \_

The first four digits are the address you plan to modify (in this example, address 1000h). The value in the parentheses is the current value for that location. The value E0 above is what you would expect immediately after loading the SIM886 program into memory. Of course, if you've previously changed the contents of memory location 1000h, it will display the current value rather than E0.

To change the contents of the specified location, simply enter an eight-bit hex constant (without the trailing "h", remember SIM886 assumes all values are hexadecimal) and press [enter]. If the value you enter is outside the range 0..FF then SIM886 will print an appropriate error message. If the value begins with a non-hexadecimal character, SIM886 will simply set the location to zero. The x86 processors only support 16-bit registers; therefore, most values you input will be 16 bits. *This means you need to enter two bytes into memory for each value*. SIM886 provides eight bit entry mainly for entering instruction opcodes.

After you hit sites SIM886 will display "1001(E0): \_" and prompt you to enter a new value for location 1001h. Each time you enter a value, SIM886 will prompt you to enter a value for the next location. When you are through entering data (or if you want to enter data at some non-consecutive address), simply hit enter without typing anything else.

#### Note: Don't forget to enter word values with the L.O. byte first and the H.O. byte second.

# 3.1 How would you display the value of memory location 18FAh in the 886 memory space using the SIM886 debugger?

# 3.2 What sequence of commands would you use to enter the word value 9837h to memory starting at location 8000h?

One last point concerning the **E**nter command which is worth mentioning: if you type a valid hexadecimal value followed by a space, SIM886 ignores the data on the line following the hexadecimal value. This allows you to type in values like the following:

E 1000 1000(00): E0 HALT instruction 1001(00): enter

The command above enters E0 into memory location 1000h. SIM886 ignores everything on the line following the E0 (in this case, the "HALT instruction" comment).

#### 3.1.2 Disassembling (Unassembling) 886 Instructions

Had you not been told that "E0" was the binary opcode for the HALT instruction you might not have ever guessed the significance of this value. All 886 instructions appear in memory as numeric values. Trying to decipher the meaning of these numeric values is quite tedious and error-prone. Fortunately, this isn't something you'll really need to do because SIM886 can do this for you automatically. The **U**nassemble command will disassemble bytes in memory producing human-readable forms of the instructions.

The Unassemble command uses the syntax:

#### U address

where *address* is the hexadecimal address of the first byte of the instruction sequence you wish to have disassembled. Since the 886 stores instruction codes in successive bytes in memory, the Unassemble command will disassemble sequential instructions. This command disassembles 15 instructions starting at the address you specify. Since instructions on the 886 are one or three bytes long, the number of bytes disassembled may be as few as 15 bytes or as many as 45 bytes.

- 3.3 If you wanted to enter the three byte instruction "ADD CX, 1" (the opcode bytes are 57 01 00) at address 1000h, what SIM886 command(s) would you use?

- 3.4 What SIM886 command would you use to view the instruction in a human readable form after entering it into the machine?

#### 3.1.3 Displaying and Modifying CPU Registers

The **R**egister command ("R") displays the current values of the 886 registers. It will display the values for AX, BX, CX, DX, and IP. It also disassembles the current instruction pointed at by IP. Unlike most debuggers, SIM886 does *not* let you modify the values of the 886's registers. In a real assembly language debugger this would be a problem. However, the programs you will be writing in 886 machine code will be very short and simple. You will not miss the ability to modify the registers. This command is mainly for tracing through programs and watching the results produced.

As it turns out, you won't use the **R**egister command to display the registers very often. The **T**race command displays the 886's registers after it steps through each instruction. You'll typically use the **R**egister command only after a disassembly or memory dump and the previous register values have scrolled off the screen.

The 886 register set usually contains zero upon initial entry into the SIM886 program. After you execute some 886 instructions the register values may change. The register set always maintains the values last stored into the registers. If you want to manually change a register value, type one of the following commands

```

RAX value

RBX value

RCX value

RDX value

```

These commands let you assign a hexadecimal value to the 886 registers.

#### 3.1.4 Executing 886 Instructions

The SIM886 Trace instruction single steps through a single instruction. The syntax for this instruction is

T address

SIM886 executes a single instruction at the specified address. After executing the instruction, SIM886 displays the registers and disassembles the next instruction in memory following the executed instruction.

Another command you can use to execute 886 instructions is the Go command. Go begins execution which stops when you press control-C or the SIM886 program encounters a HALT instruction:

G address

begins execution at the specified address

#### 3.1.5 File I/O Commands

SIM886 provides three commands to let you read data from a text file and write data to a text file on the disk. The Input command takes the following form:

```

I filename

```

*Filename* must be a valid DOS pathname. The **I**nput command tells SIM886 to read the next set of keyboard commands directly from the file rather than the keyboard. When SIM886 encounters the end of this file, it reverts input back to the keyboard. The primary purpose for the **I**nput command is to allow you to create an 886 assembly language program with a text editor (such as DOS' EDIT program) and then read this file into SIM886. A typical source file you would create with an editor might look like the following:

```

A 0

load ax, 0

load bx, 1

add ax, bx

u 0

```

Note the "A 0" command as the first line of this file. Remember, after processing the Input command, SIM886 is going to try to read another command from the standard input. Since the input is coming from the file, the file must contain the command that activates the SIM886 assembler. The "u 0" command instructions SIM886 to unassemble this code after assembling it.

The other two file commands in SIM886 let you capture all output that goes to the screen and send a copy of it to a DOS text file. This provides a convenient way to capture the output of a SIM886 session without using the Ctrl P option to send the output to a printer. This allows you, for example, to create a text file transcription you can import into the word processor you're using to create your lab report.

To begin capturing data, use the "C *filename*" command. From that point forward, all data written to the screen is also written to the output file. To turn off the capture operation, use the "X" command.

#### 3.1.6 Miscellaneous SIM886 Commands and Other Notes

If you forget one of the SIM886 commands, you can get an instant refresher using the SIM886 *help* command. Pressing the question mark ("?") displays a list of the available commands with a brief description of their syntax and operation. Furthermore, if any new commands have been added since the publication of this manual, or if your local installation has added some special commands, the help command will tell you about them.

When you are done using SIM886, you can return to MS-DOS using the  $\mathbf{Q}$ uit command. Simply press "Q" followed by enter at the SIM886 prompt to quit the program. Note that if you restart the SIM886 program after quitting it, you lose everything in the 886 memory space. You will have to reenter such values if you need them.

| On all of the SIM886 commands, the address following the command is optional. If you do not supply an address, SIM886 will look at the last time you used that command and supply the next available address for the current command. For example, if you use the command "D 1000" to dump memory locations 1000100F and then press "D enter", SIM886 will automatically supply the value 1010 for you.                                                                                                                                                                                                                                                                                                                                                                                 | 3.1 | D 18FA                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------|

| SIM886 remembers the last address for each specific command. If you enter the commands "D 1000" followed by "U 2000" and then press "D enter", SIM886 will display locations 1010101F, <i>not</i> the bytes following the last disassembled instruction. Likewise, were you to enter the command "U œ" at this point, it would continue the disassembly after the previous instruction, it would not begin the disassembly at address 1020. SIM886 maintains separate <i>current address</i> values for the D, E, U, and X commands.                                                                                                                                                                                                                                                    | 3.2 | E 8000<br>37<br>98       |

| Another useful shortcut is the enter command. If you press the enter key by itself on a SIM886 command line, it repeats the last instruction at the new address. For example, if you enter the command "D 1000 enter" and then press enter, SIM886 will repeat the memory dump command beginning at location 1010. Repeatedly pressing enter will dump memory locations 1020102F, 1030103F, etc. This "repeat last command" operation is particularly useful with the Trace command. After you use the "T" command to execute the first instruction, repeatedly pressing enter will single step through the following instructions.                                                                                                                                                     |     |                          |

| The "W <i>count</i> " command lets you specify the number of <i>wait states</i> SIM886 will use on each memory access. By default, SIM886 uses zero wait states so accessing memory at an even address requires only one clock cycle. You can change the number of wait states using this command. Like all SIM886 commands, the numeric value you specify is a <i>hexadecimal</i> number. Don't forget this if you want to specify more than nine wait states. If you enter the "W" command without any parameters, SIM886 defaults back to zero wait states. If you want to see the current number of wait states that SIM886 is using, use the <b>R</b> egister command to display the register values. The "WS" register specifies the number of wait states on each memory access. | 3.3 | E 1000<br>57<br>01<br>00 |

| SIM886 maintains a global clock cycle counter. After executing each instruction SIM886 adds the number of clock cycles for that instruction to this global counter. This lets you trace through a sequence of instructions and determine how many clock cycles occurred during the execution of those instructions. You can view the global clock cycle counter by using the <b>R</b> egister command. The "Z" (for <b>Z</b> ero) command resets this global clock cycle counter to zero. If you want to time a sequence of instructions, you should reset the global cycle counter before executing those instructions.                                                                                                                                                                | 3.4 | U 1000                   |

| 3.2 Machine Language vs. Assembly Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |                          |

| As you may have noticed, there isn't a command in SIM886 to enter 886 instructions into memory. You can execute instruction using the <b>T</b> race command, but there isn't a command (described yet) to let you type something like "LOAD AX,0" into the debugger. Well, it turns out that the 886 processor (hypothetical or otherwise) does <i>not</i> execute instructions like "LOAD AX,0". Instead, it executes numeric encodings of these instructions. The "LOAD AX,0" instruction actually consists of three one byte values: 07 00 00. These three values tell an x86 processor to load the AX register with zero. These numeric forms of the instruction are <i>machine</i>                                                                                                 |     |                          |

instruction actually consists of three one byte values: 07 00 00. These three values tell an x86 processor to load the AX register with zero. These numeric forms of the instruction are *machine code*– instructions specifically for the machine. The human-readable form, "LOAD AX,0", is *assembly language*<sup>2</sup>. As you can probably tell, it's much easier to work in assembly language than in machine language. Although "LOAD AX,0" might not be the most understandable command you've ever seen, it's probably a lot easier to read and understand than " 07 00 00".

<sup>2.</sup> The term "assembly language" came about because the process of converting assembly code to machine code traditionally consists of building (or *assembling*) binary machine code instructions from various bit patterns which make up the instruction, operands, and addressing modes.

Most of the time you will be working in assembly language. This is, after all, an assembly language text, not a machine language text. However, it's definitely worthwhile to spend a little time working with machine language. This achieves three things: (1) it gives you an appreciation for what the assembler does for you; (2) many debugging problems require that you work at the machine level; and, most importantly, (3) working at the machine level forces you to take a close look at the underlying architecture, which you might be able to ignore at the assembly level.

The 80x86 processor family is quite complex and difficult for beginners to understand at the machine level. Indeed, that's the whole reason for introducing the x86 hypothetical processors in this text. The x86 family is very simple. Its design helps demonstrate important architectural features without being laden down with 1976 design decisions<sup>3</sup>. None-theless, Much of what you learn concerning the 886 applies almost directly to the 80x86 family as well.

# 3.5 Given that the machine code for "LOAD AX,0" is 07 00 00, what SIM886 command would you use to enter this instruction into memory at address 2000h?

#### 3.3 A Review of the 886 Instruction Set

The x86 processor family supports eleven different instructions. They are LOAD, STORE, ADD, SUB, IFEQ, IFLT, IFGT, HALT, GOTO, GET, and PUT. With the exception of the HALT instruction, all of these instructions require one or more operands.

The LOAD, STORE, ADD, and SUB instructions all have identical operands. These instructions take the form:

instr reg, operand

where "instr" is any of "LOAD", "STORE", "ADD", or "SUB"; "reg" is any of "AX", "BX", "CX", or "DX"; and operand is one of "AX", "BX", "CX", "DX", "[BX]", "const[BX]", "[const]", or "const".

The LOAD instruction makes a copy of the second operand and places it in the first operand. This instruction overwrites the value of the first operand and does not affect the value of the second operand. You generally use this instruction to copy a value from memory into one of the four 886 general purpose registers, although you can use it to copy data from one register to another as well.

The second operand (the source of the data to copy to the first operand) can be one of the four registers, a memory address, or a constant. Quickly, here's what each of the forms of this instruction do:

| LOAD | ax, | ax | ;Produce | es no d | obse | erva | able 1 | resul | lts! |      |

|------|-----|----|----------|---------|------|------|--------|-------|------|------|

| LOAD | ax, | bx | ;Copies  | value   | in   | ВΧ   | into   | the   | AX   | reg. |

| LOAD | ax, | CX | ;Copies  | value   | in   | СХ   | into   | the   | AX   | reg. |

| LOAD | ax, | dx | ;Copies  | value   | in   | DX   | into   | the   | AX   | reg. |

(Note that you may substitute BX, CX, or DX for the first operand above to load the specified value into BX, CX, or DX rather than AX. For example "LOAD bx, ax" copies the value in the AX register into BX.)

| LOAD | ax, | [bx]   | ;Copies data from memory location "bx"<br>; into ax.                                         |

|------|-----|--------|----------------------------------------------------------------------------------------------|

| LOAD | ax, | nn[bx] | ; Copies data from memory location "bx +<br>; nn" into ax. "nn" represents a 16-bit          |

| LOAD | ax, | [nn]   | ; constant.<br>;Copies data from memory location "nn"<br>; into ax. "nn" represents a 16-bit |

| LOAD | ax, | nn     | ; constant.<br>;Copies 16-bit constant "nn" into ax.                                         |

These last four forms of the LOAD instruction probably deserve a little more explanation. The first three of these introduce different *memory addressing modes*. That is, they provide different ways of accessing memory. The first of these, "[BX]" is typically referred to as the *indirect addressing mode*. This addressing mode does not copy the value of BX into AX. That would be *direct* addressing. Instead, BX contains a value which the instruction uses as the memory address

<sup>3.</sup> If you hadn't guessed, the 8086 was first developed in 1976. Many of the complexities of the 80x86 family stem from the fact that the original 8086 designers didn't expect their processor to last so long in the marketplace.

of the actual value to fetch. For example, if BX contained 1800h, "LOAD ax, [bx]" would load ax with the word value beginning at memory address 1800h.

The second memory addressing mode above is the *indexed addressing mode*. As you'll see in Chapter Four, this addressing mode is particularly useful for accessing elements of arrays and records. This address mode adds the value contained in BX with the 16-bit constant specified by "nn". The 886 uses their sum as the *effective address* and loads the specified register (AX in this case) with the 16-bit value starting at that address.

The third memory addressing mode, "[nn]", is the *direct addressing mode*. The second operand is just a 16-bit constant which provides the memory address to fetch and load into the destination register (AX in this case). You would use this addressing mode, for example, to access 16bit variables in memory.

The last addressing mode isn't really a memory addressing mode, it's the immediate addressing mode which lets you load constants into a register. The "LOAD ax, nn" instruction (assuming "nn" represents a 16-bit hexadecimal constant) load the AX register with the value "nn". For example, "LOAD ax, 0" loads the AX register with zero.

As mentioned earlier, the STORE, ADD, and SUB instructions allow the same operands as the LOAD instruction. The STORE instruction is the converse operation to LOAD. It stores the first operand to the location specified by the second operand. Note that the STORE instruction does *not* allow the immediate addressing mode (it doesn't make sense to store a register into a constant). ADD and SUB, however, allow all addressing modes. Note that certain LOAD and STORE instructions perform the same operation. "LOAD ax, bx", for example, does the same thing as "STORE bx, ax".

The ADD instruction adds the value specified by the second operand to the first operand leaving the result in the first operand. The SUB instruction subtracts the second operand from the first operand leaving the result in the first operand. Both instructions allow all eight possible addressing modes for the second operand (four register modes, three memory modes, and the immediate mode).

The IFEQ, IFGT, and IFLT instructions all take three operands:

$reg_1$  and  $reg_2$  represent one of the four 886 registers: AX, BX, CX, or DX. "nn", as usual, represents a 16-bit constant. These instructions compare  $reg_1$  to  $reg_2$ . For IFEQ, if the two registers are

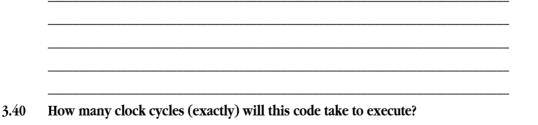

| i i i r                     | r m m m                                      |                                                                  |

|-----------------------------|----------------------------------------------|------------------------------------------------------------------|

| iii r                       | r mmm                                        | Note, this 16 bit operand is present only if mmm is 101,         |

|                             | 00 = AX $0 = AX01 = BX$ $0 = AX0 = BX$       | 110, or 111 or if iii is 100,<br>101, 110, or 111; if iii is     |

| 010 = add                   | 0 = CX $0 = CX1 = DX$ $0 = CX0 = DX$         | 100, 101, or 110, then mmm                                       |

| 100 = ifeq<br>101 = iflt    | $1 \ 0 \ 0 = [BX]$<br>$1 \ 0 \ 1 = xxxx[BX]$ | may only be 000, 001, 010, or 011. If iii is 111 then the        |

| 110 = ifgt<br>111 = special | 1 1 0 = [xxxx]<br>1 1 1 = constant           | instruction uses a special<br>encoding described else-<br>where. |

X86 Instruction Encoding

equal, the 886 loads the IP register with the constant. If the two registers are not equal, the 886 ignores the constant. IFGT and IFLT work in a similar manner except they load IP with the constant if  $reg_1$  is greater than  $reg_2$  or  $reg_1$  is less than  $reg_2$ , respectively. Note that loading the IP (instruction pointer) register with "nn" will interrupt the normal flow of execution. Instead of executing the instruction following IFEQ, IFGT, or IFLT, the 886 will execute the instruction at address "nn" if the IFxx instruction loads IP with "nn". For this reason, these are *transfer of control* instructions.

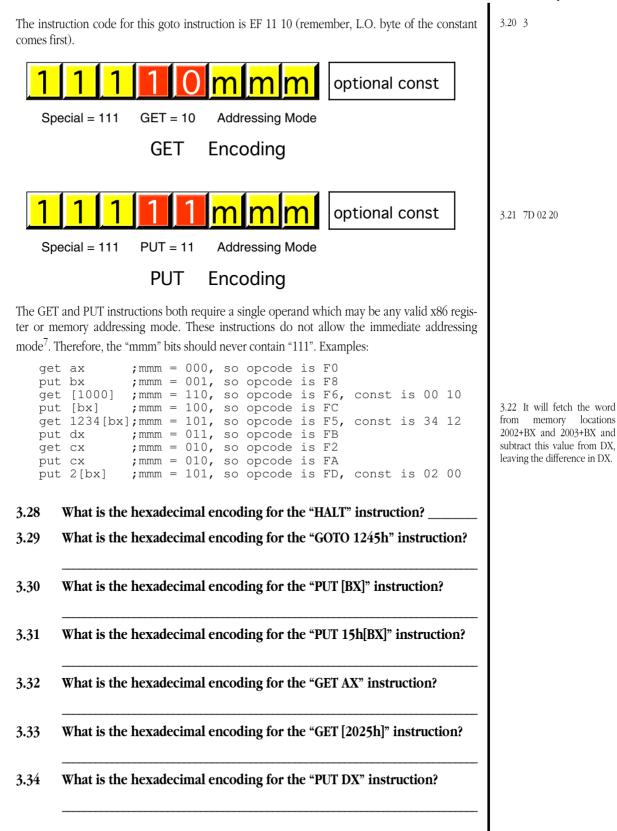

The GET and PUT instructions let you perform simple I/O when running 886 programs. They both accept a single operand which is identical to the second operand of the STORE instruction (that is, a register or a memory addressing mode).

The GET instruction stops execution and prompts you to enter a value (in hexadecimal) from the keyboard. The PUT instruction outputs the specified value to the screen. The GET instruction is particularly useful for loading different values into registers while the program is running. Although the GET instruction allows a memory addressing mode, using the GET instruction to read a value into a memory location is of marginal utility. After all, you can use the SIM886 Enter instruction to accomplish the same thing. Of course, were you to modify SIM886 to execute more than one instruction at a time, this instruction would be more useful.

The PUT instruction outputs the specified register or memory operand. Since SIM886 displays the contents of all 886 registers after executing each instruction, using PUT to output a register value won't buy you much. It is quite handy for output memory locations, however (this saves you the effort of using the SIM886 **D**ump command).

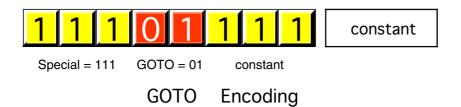

The GOTO instruction must be followed by a 16-bit constant. This instruction loads the IP register with the value of the constant. Like the IFxx instructions, the GOTO instruction is a transfer of control instruction. The IFxx instructions are *conditional transfer instructions* since they transfer control (or not) based on some condition being true. The GOTO instruction is an *unconditional transfer instruction* since it transfers control regardless of any condition which may or may not exist.

The HALT instruction is the only 886 instruction which doesn't require any operands. When SIM886 encounters this instruction it stops processing. The HALT instruction does not update the IP to point at the next instruction. If you execute HALT and immediately specify the e**X** ecute instruction again (without specifying a new address) will execute the same HALT instruction.

- 3.6 How could you copy the contents of memory locations 1000/1001h to memory locations 8000/8001h using 886 instructions? (hint: feel free to use more than one instruction if necessary)

- 3.7 Write a short 886 program which inputs a value from the keyboard and sets AX to zero if the value is less than 8000h or sets AX to 1 if the input value is greater than or equal to 8000h, then halts.

E 2000

07 00 00

3.5

### 3.4 Converting 886 Programs to Machine Code

The preceding section described the operation of the 886 processor in terms of assembly language. Alas, you've already been told that SIM886 doesn't support assembly language, only machine code. This means you've got to convert nice, readable (!), instructions like "LOAD AX,0" into sequences of numbers like "07 00 00" before you can enter the instruction into SIM886. The question is "How on Earth does someone memorize all the possible instruction codes?" The answer is quite simple– you don't. Instead, you *assemble* the instruction opcodes yourself using some relatively simple look ups.

The 886 processor uses a relatively simple instruction encoding scheme. All 886 instructions use the encodings below. All opcodes are one byte long. All instructions are one or three bytes long (the extra two bytes in the three-byte instructions hold the 16-bit constants appearing in 886 instructions). The opcode byte always appears first in memory (that is, at the lowest address). If a 16-bit constant follows the opcode, the L.O. byte of the constant comes first followed by the H.O. byte.

Bits zero through two of the opcode byte contain the addressing mode for the second operand. Bits three and four encode the value for the first register operand. Bits five through seven encode the instruction itself.

As simple as the 886 instruction encoding scheme is, there are still some inconsistencies of which you must be aware. For example, the 886 has eleven different instructions, but only three bits to encode the instructions. Three bits lets you specify eight different instructions, not eleven. To get around this, the 886 uses a special instruction encoding, iii=111 (the *special* entry above) to *extend* the instruction set. When the opcode field contains 111, the register field determinates the actual instruction. The for possible values are

00 - Halt 01 - Goto 10 - Get 11 - Put

Since these instructions use the register operand field to encode the operation, there is only one field left for the operand. Goto, get, and put only allow a single operand, so this works out well. Halt does not allow any operands, so if the H.O. five bits of the opcode contain 11100, SIM886 ignores the L.O. three bits (the second operand field).

Finally, consider the IFxx instructions. They have *three* operands. How does the encoding above handle them? Easy. The register and operand fields (bits 0..4) encode two registers. The third operand is a displacement, so these instructions always include a 16 bit displacement value after the opcode.

## 3.4.1 Encoding the LOAD, STORE, ADD, and SUB Instructions

The LOAD, STORE, ADD, and SUB instructions are the easiest to handle, so they're the best place to start. With one single exception, these four instructions implement the encoding above exactly. The only exception is that the encoding above allows a machine code instruction of the form "27 00 00" which corresponds to a "STORE reg, immediate" instruction. Since there is no such thing as a store immediate instruction, we have a problem. To solve this problem the 886 adopts the same strategy as most processors– it treats this as an illegal instruction which programmers are not supposed to put into the program. Doing so may produce an error or unpredictable results.

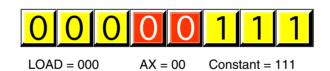

To convert the "LOAD AX, 0" instruction to its equivalent machine code, the first step is to construct the opcode for this instruction:

• Since this is the LOAD instruction, bits five through seven of the opcode must be 000.

- The register operand (the first operand) is AX. The bit code for this operand is 00 (for bits three and four).

- Finally, this instruction uses the immediate (constant) addressing mode. Bits zero through two must contain 111 for the immediate addressing mode.

- Two additional bytes containing the immediate constant (0000h) must follow the opcode.

This yields the following opcode:

# LOAD AX, 0 Encoding

Two bytes of zeros, representing the 16-bit immediate constant, must follow the opcode low order byte first. Therefore the complete instruction is three bytes long and is 07 00 00. So now you can see where these "magical" numbers came from.

For LOAD, STORE, ADD, and SUB, if the addressing mode is 101, 110, or 111 (xxxx[bx]. [xxxx],. or constant) then there will be a 16-bit constant following the opcode (L.O. byte first). All other forms of these instructions are one byte long. Some additional examples will help cement this down.

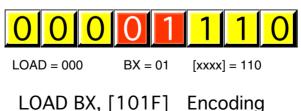

Consider the "LOAD BX, [101F]" instruction. You build the opcode as follows:

- Since this is the LOAD instruction, bits five through seven of the opcode must be 000.

- The register operand (the first operand) is BX. The bit code for this operand is 01 (for bits three and four).

- Finally, this instruction uses the direct ([xxxx]) addressing mode. Bits zero through two must contain 110 for the immediate addressing mode.

- Two additional bytes, containing 101Fh, must follow the opcode (1F first, 10 second).

This yields the following opcode:

- 3.8 How many bytes long is this instruction?

- 3.9 What is the hexadecimal machine code encoding for this instruction?

- 3.10 What will this instruction do when the 886 executes it?

#### 3.11 What would the encoding be for "LOAD DX, [101F]"?

Consider the "STORE AX, BX" instruction:

- Since this is the STORE instruction, bits five through seven of the opcode must be 001.

- The register operand (the first operand) is AX. The bit code for this operand is 00 (for bits three and four).

- This instruction uses the register/BX addressing mode. Bits zero through two must contain 001 for BX.

The opcode is

#### 80x86 Based Systems

3.6 One way to do it: Load ax, [1000] Store ax. [8000]

3.7 One way to do it: get bx load cx. 8000 iflt bx. cx. Set0 load ax. 1 goto Done

Set0: load ax, 0 Done: halt

Note: Set0 and Done represent the addresses of the corresponding "labels" in this short program. If this code where assembled at address zero, Set0 would be equal to address 000Dh and Done would be equal to address 0010h.

## STORE AX. BX Encoding

- How many bytes long is this instruction? 3.12

- What is the hexadecimal machine code encoding for this instruction? 3.13

- What will this instruction do when the 886 executes it? 3.14

- What is another instruction which performs the exact same operation 3.15 as this instruction?

#### What is the hexadecimal encoding for that other instruction? 3.16

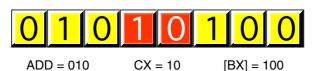

Moving on to the ADD instruction, consider the encoding for the "ADD CX, [BX]" instruction:

- Bits five through seven of the opcode must be 010 for the ADD instruction. .

- The register operand (the first operand) is CX. The bit code for this operand is 10 (for bits three and four).

- This instruction uses the [BX] addressing mode. Bits zero through two must con-. tain 100 for [BX].

The opcode is

ADD CX, [BX] Encoding

- 3.17 How many bytes long is this instruction?

- 3.18 What is the hexadecimal machine code encoding for this instruction?

- What will this instruction do when the 886 executes it? 3.19

STORF = 001AX = 00BX = 001

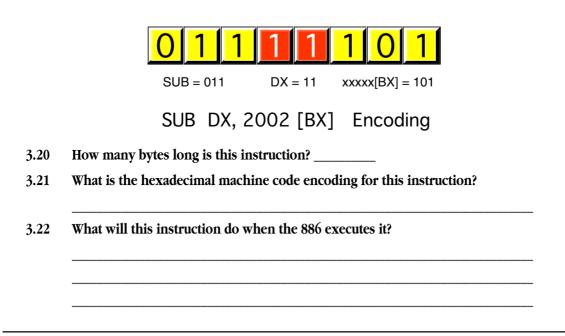

Finally, consider the "SUB DX, 2002 [BX]" instruction. Its encoding is

- Bits five through seven of the opcode must be 011 for the **sub** instruction.

- The register operand (the first operand) is dx. The bit code for this operand is 11 (for bits three and four).

- This instruction uses the indexed (xxxx[BX]) addressing mode. Bits zero through two must contain 101 for xxxx[BX].

- Two displacement bytes containing the value 2002h (02 first, 20 second) must follow the opcode.

The opcode is

#### 3.4.2 Encoding the IFEQ, IFLT, and IFGT Instructions

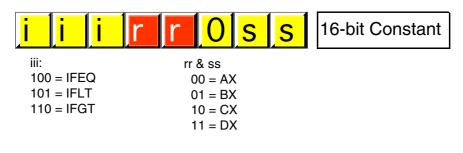

The  $\mathbf{i} \mathbf{f} \mathbf{x} \mathbf{x}^4$  instruction encodings do not follow the same exact form as load, store, add, and sub. Considering that the  $\mathbf{i} \mathbf{f} \mathbf{x} \mathbf{x}$  instructions have three operands, this shouldn't be too surprising. The generic encoding for the  $\mathbf{i} \mathbf{f} \mathbf{x} \mathbf{x}$  instructions is

## IFxx reg, reg, constant Encoding

Note that bit two *must be zero*. IFxx instructions containing a one in this bit position are illegal instructions. Also note that a 16-bit constant *always* follows the instruction, regardless of the opcode, hence all ifxx instructions are three bytes long.

Bits three and four in the opcode supply the value for the first register operand. Bits zero and one supply the value for the second register operand. Since these are the only encodings available, the first two operands *must* be registers.

<sup>4.</sup> IFxx represents any of the three instructions IFEQ, IFLT, or IFGT.

# 80x86 Based Systems

| The third operand is always a 16-bit constant, therefore the opcode doesn't need any extra bits to inform the x86 processor that the word following the opcode is a constant.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3.8 3                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Remember, the x86 processors compare the two register operands and then transfer control to the address specified by the 16-bit constant if the contents of the registers are equal (ifeq), less than (if1t), or greater than (ifgt). Algorithmically, we can describe the operation of these instructions as follows:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3.9 OE 1F 10                                         |

| ifeq $reg_1$ , $reg_2$ , constant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                      |

| <pre>if (reg<sub>1</sub> = reg<sub>2</sub>) IP := constant else IP := IP + 3;</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.10 Load the BX register with a copy of the data at |

| iflt reg <sub>1</sub> , reg <sub>2</sub> , constant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | memory locations 101F/                               |

| <pre>if (reg<sub>1</sub> &lt; reg<sub>2</sub>) IP := constant else IP := IP + 3;</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1020.                                                |

| ifgt reg1, reg2, constant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                      |

| <pre>if (reg1 &gt; reg2) IP := constant else IP := IP + 3;</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3.11 1E 1F 10                                        |

| Were you to place a one in bit number two of the opcode, the x86 processor might confuse<br>the 16-bit constant following the opcode with one of the 16-bit constants required by the mem-<br>ory or immediate addressing modes. This is why bit number two must always contain zero.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3.12 1                                               |

| As a short digression, it's worth mentioning <i>why</i> the x86 processors require that the second operand be zero. Since we have the bit available, you might ask "Why not allow those extra addressing modes?" Of course, three of the extra addressing modes require their own 16-bit constant but that could be easily handled by extending the instruction to five bytes in such cases. However, doing so would complicate the instruction set, something which tends to defeat the purpose of the 886 in the first place. On the other hand, limiting the operands in this manner forces you to memorize which instructions allow memory/immediate operands and which do not. Proceeding the user the arms operands for all instructions have memory are user to use the arms operands for all instructions have memory and the advectory of the set of the set of the advectory operands and which do not proceeding the advectory operands for all instructions have memory and the advectory operands for all instructions have memory and the advectory operands for all instructions have memory and the advectory operands for all instructions have memory advectory operands for a line operands advectory operands advectory operands for a line operands advectory operands and which do advectory operands advectory operand | 3.13 21                                              |

| not. Processors which allow you to use the same operands for all instructions have <i>regular</i> or <i>orthogonal</i> instruction sets. The x86 processors do not allow all possible forms for each operand, so they are not completely orthogonal <sup>5</sup> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3.14 3Copy the value in AX to the BX register.       |

| Now consider the encoding for the ifgt dx, bx, 8098 instruction:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                      |

| <ul> <li>Bits five through seven of the opcode must be 110 for the ifgt instruction.</li> <li>The first register operand is dx. The bit code for this operand is 11 (for bits three</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3.15 Load BX, AX                                     |

| <ul> <li>and four).</li> <li>The second register operand is bx. Bits zero through two must contain 010 for bx.</li> <li>Two displacement bytes containing the value 8098h(98 first, 90 second) must follow the opcode.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3.16 28                                              |

| The opcode is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3.17 1                                               |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3.18 54                                              |

| IFGT DX, BX, 8098h Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                      |