# Capítulo 5.

# Ayuda del programa

En este capítulo se describe el uso de la aplicación haciendo un recorrido sobre el fichero de ayuda incluido en el mismo.

# 5.1. Instalación y ejecución del programa

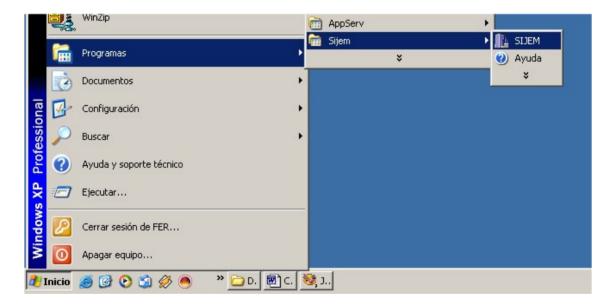

La distribución del simulador incluye un programa de instalación que tras su ejecución muestra dos nuevos accesos directos a la aplicación y su ayuda en el menú inicio.

Captura 5.1. Inicio del programa SIJEM y su Ayuda

Haciendo clic sobre SIJEM accedemos a la aplicación, mientras que haciendo clic sobre Ayuda accedemos al archivo de ayuda.

# 5.2. Archivo de ayuda

En las siguientes páginas se muestran las diferentes secciones del archivo de ayuda.

Al iniciar la ayuda nos encontramos con la siguiente pantalla, que nos muestra las diferentes secciones:

#### Bienvenido

- Introducción a SIJEM

- Interfaz de usuario

- Ficheros

#### 5.2.1. Introducción a SIJEM

SIJEM es un simulador didáctico de jerarquías de memoria.

Su objetivo es servir de apoyo al aprendizaje de los conceptos de jerarquías de memoria, fundamentales en materias como Sistemas Operativos y Arquitectura de Computadores.

A través de un interfaz altamente visual trata de ilustrar los siguientes conceptos de jerarquías de memoria:

#### Memoria virtual

- Direcciones virtuales y direcciones reales.

- Paginación

- Mecanismos de traducción de direcciones.

- Uso de TLBs.

- Estrategias de búsqueda, colocación y reemplazamiento en memoria principal.

## Niveles de memoria

- Memoria secundaria.

- Memoria principal.

- Memoria caché multinivel.

- Nivel 3

- Nivel 2

- Nivel 1 Conjunta o separada en datos e instrucciones.

- Estrategias de colocación, reemplazamiento y coherencia entre los diferentes niveles.

Y haciendo uso de ficheros de traza procedentes de la ejecución de programas reales o inventados por el usuario obtenemos resultados como:

- Tiempo de ejecución del programa en ciclos.

- Tiempo empleado en acceder a un dato/instrucción en ciclos.

- Tasa de aciertos y fallos en memoria principal y memoria caché.

- Número de instrucciones de cada tipo contenidas por un programa.

- Número de reemplazamientos en memoria principal y memoria caché.

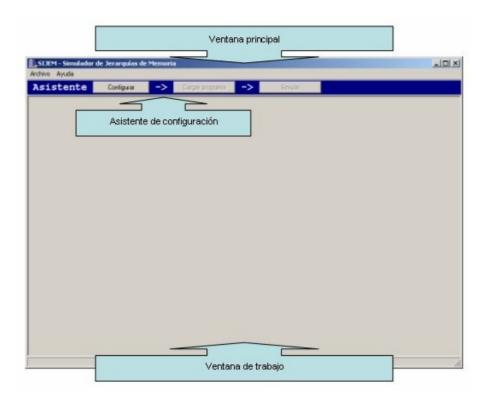

## 5.2.2. Interfaz de usuario de SIJEM

La interfaz de usuario de SIJEM se compone de:

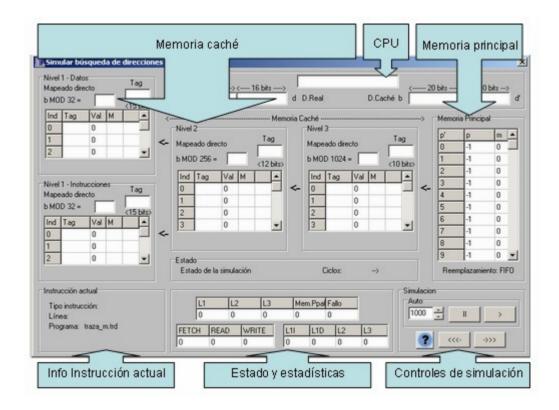

Captura 5.2. Interfaz de usuario

- Ventana principal

- Es la ventana principal del programa dentro de la cual se ejecuta el mismo.

- Asistente de configuración

Se compone de tres botones

- Configurar

- Cargar programa

- Simular

que ayudan en la ejecución del simulador.

Además existe el botón de "Resumen Configuración", activo en las etapas de cargar programa y simular, para obtener un resumen de la configuración efectuada.

• Ventana de trabajo

En ella se muestran las diferentes ventanas con las que trabaja el programa.

## 5.2.2.1. Asistente - Configurar

Al pulsar sobre el botón configurar del asistente se nos muestran una serie de ventanas que nos ayudarán en la tarea de ejecución del simulador.

#### Estas ventanas son:

- Bienvenido Introducción a las páginas de configuración.

- Página 1 Cargar fichero y configurar memoria principal y secundaria.

- Página 2 Mecanismo de traducción de direcciones y paginación.

- Página 3 Caché de nivel 3.

- Página 4 Caché de nivel 2.

- Página 5 Caché de nivel 1.

- Página 6 Resumen de la configuración elegida.

A través de estas páginas iremos configurando nuestro simulador para realizar la simulación elegida.

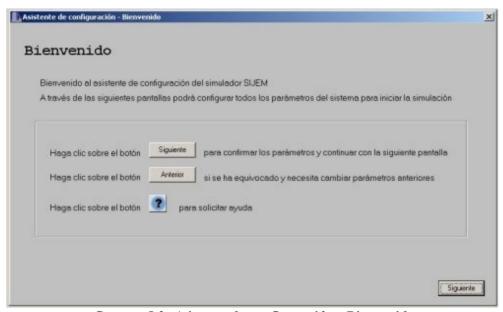

# A. Asistente > Configurar > Bienvenido

Al hacer clic sobre el botón configurar del asistente se visualiza esta ventana que nos muestra la serie de pautas a seguir para configurar la ejecución del simulador.

#### Tales como:

- Hacer clic sobre el botón "Siguiente" para confirmar los parámetros y continuar con la siguiente pantalla.

- Hacer clic sobre el botón "Anterior" si se ha equivocado y necesita cambiar parámetros anteriores.

- Hacer clic sobre el botón "Ayuda" para solicitar ayuda.

Captura 5.3. Asistente de configuración - Bienvenido

Al hacer clic sobre el botón "Siguiente" pasamos a la página 1 de la configuración.

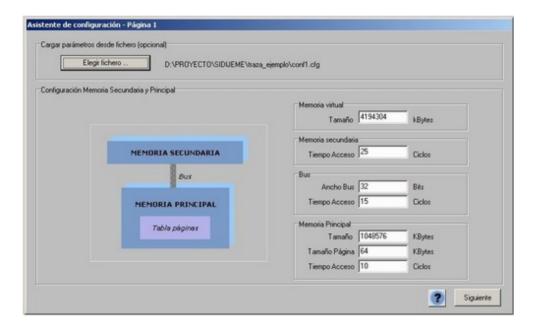

## B. Asistente > Configurar > Página 1

A través de esta ventana podemos:

- Cargar un fichero de configuración.

- Configurar los parámetros de la memoria principal y de la memoria secundaria.

Captura 5.4. Asistente de configuración – Página 1

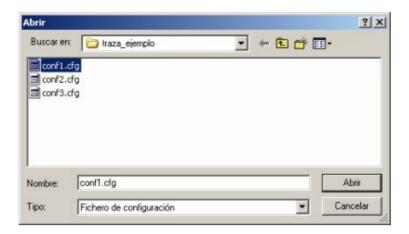

# B.1. Asistente > Configurar > Página 1. Cargar un fichero de configuración

El simulador permite cargar todos los parámetros de configuración desde un fichero previamente realizado por el usuario, u obtenido de entre los múltiples ejemplos contenidos en el paquete.

La estructura de este fichero se define en la sección ficheros.

Para cargar un fichero de configuración haremos clic sobre el botón "Elegir fichero" contenido en el cuadro de texto "Cargar parámetros desde fichero".

A continuación se nos mostrará un cuadro de diálogo para elegir el fichero .cfg que deseamos cargar, hacemos clic sobre el botón "Aceptar" y si se trata de un fichero válido los parámetros serán volcados a los diferentes cuadros de configuración. Y junto al botón "Elegir fichero" se mostrará la ruta del fichero elegido.

Captura 5.5. Carga de un fichero de configuración

Al hacer clic sobre el botón "Siguiente" pasamos a la página 1 de la configuración.

# B.2. Asistente > Configurar > Página 1. Configurar los parámetros de la memoria principal y de la memoria secundaria.

A través de esta página de configuración fijamos los siguientes parámetros:

## • MEMORIA VIRTUAL

• Tamaño (en Kbytes): Tamaño del espacio de direcciones que puede ser referenciado por el programa en ejecución.

#### MEMORIA SECUNDARIA

• Tiempo de acceso (en ciclos): Tiempo empleado para acceder a una página situada en la memoria secundaria.

## • BUS MEMORIA SECUNDARIA - MEMORIA PRINCIPAL

- Ancho bus (en bits): Ancho del bus situado entre memoria principal y memoria secundaria.

- Tiempo de acceso (en ciclos): Tiempo empleado para trasladar una palabra entre la memoria secundaria y la memoria principal a través de este bus.

## • MEMORIA PRINCIPAL

- Tamaño (en Kbytes): Tamaño físico de la memoria principal.

- Tamaño de página (en Kbytes): Tamaño de la página de memoria.

- Tiempo de acceso (en ciclos): Tiempo empleado para acceder a una página situada en la memoria principal.

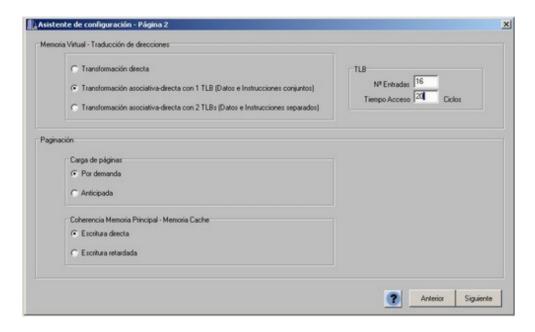

## C. Asistente > Configurar > Página 2

A través de esta ventana podemos:

- Establecer el mecanismo de traducción de direcciones virtuales en direcciones reales.

- Definir los parámetros de la paginación.

Captura 5.6. Asistente de configuración – Página 2

## C.1. Asistente > Configurar > Página 2. Mecanismo de traducción de direcciones

A través de este cuadro fijamos el mecanismo de traducción de direcciones de memoria virtual a direcciones reales de memoria.

## Podemos elegir entre:

## • TRANSFORMACIÓN DIRECTA

La tabla de mapa de páginas contiene una entrada para cada una de las páginas de la memoria virtual de este programa.

## • TRANSFORMACIÓN ASOCIATIVA-DIRECTA CON 1 TLB

Junto con la tabla de páginas existe una memoria asociativa denominada TLB (Translation Lookaside buffer) que contiene las traducciones más recientes.

## • TRANSFORMACIÓN ASOCIATIVA-DIRECTA CON 2 TLB

Es similar a la anterior, pero usando dos memorias asociativas, una para las traducciones más recientes de búsqueda de instrucciones (TLB de instrucciones) y otra para las traducciones más recientes de lectura o escritura de datos (TLB de datos).

Si elegimos cualquiera de estas dos últimas opciones debemos configurar los parámetros de la TLB:

- Número de entradas de la TLB: Número de entradas que tendrá la TLB. Si se selecciona 2 TLB será el número de entradas de cada TLB.

- Tiempo acceso: Tiempo empleado para acceder a una entrada de la TLB.

# C.2. Asistente > Configurar > Página 2. Paginación

A través de este cuadro fijamos los siguientes parámetros:

# • MECANISMO DE CARGA DE PÁGINAS

- *Por demanda:* Las páginas se van cargando en memoria a medida que van siendo solicitadas por el programa en ejecución.

- *Anticipada:* Además de la página solicitada por el programa en ejecución se carga la siguiente página de memoria.

# • COHERENCIA ENTRE MEMORIA CACHÉ Y MEMORIA PRINCIPAL

- Escritura directa: La escritura de una página situada en memoria caché implica que la copia de memoria principal se actualice inmediatamente. Dado que se utiliza una estructura basada en Victim Buffer esta actualización no conlleva ciclos de CPU.

- Escritura retardada: La copia en memoria principal sólo es actualizada cuando la página es reemplazada en memoria caché. En este caso, cuando una página es reemplazada, debemos esperar a que la copia en memoria principal sea actualizada, lo que implica que se tenga que esperar tantos ciclos como una escritura en memoria principal.

## D. Asistente > Configurar > Página 3

A través de esta página configuramos el tamaño del bloque de caché y los siguientes parámetros de la caché de nivel 3:

- Habilitar o deshabilitar este nivel de memoria.

- Definir la organización.

- Establecer el número de conjuntos.

- Establecer la política de reemplazamiento.

- Definir los parámetros de la memoria.

- Definir los parámetros del bus.

Captura 5.7. Asistente de configuración – Página 3

## D.1. Asistente > Configurar > Página 3. Caché de nivel 3. Habilitar

Especifica el tamaño del bloque de caché en bytes.

## D.2. Asistente > Configurar > Página 3. Caché de nivel 3. Habilitar

A través de este cuadro habilitamos o deshabilitamos el uso de la memoria caché de nivel 3.

Si deshabilitamos la memoria caché de nivel 3 el resto de los parámetros de la página dejan de estar disponibles pues pierden su significado.

## D.3. Asistente > Configurar > Página 3. Caché de nivel 3. Organización

A través de este cuadro fijamos la organización de este nivel de memoria.

Podemos elegir entre:

## • MAPEADO DIRECTO

Cada bloque tiene un sólo lugar donde ser colocado en memoria caché según la fórmula

(Página de memoria principal) MOD (Número de bloques en caché)

#### COMPLETAMENTE ASOCIATIVA

Cada bloque puede ser colocado en cualquier lugar de la memoria caché.

#### ASOCIATIVA POR CONJUNTOS

A cada bloque le corresponde un conjunto dentro de memoria caché, de manera que puede ser colocada en cualquier posición dentro del conjunto, según la formula:

(Bloque de memoria caché) MOD (Número de conjuntos en caché)

Si un conjunto tiene n bloques se denomina Memoria Asociativa por Conjuntos de N-Vías.

## D.4. Asistente > Configurar > Página 3. Caché de nivel 3. Número de conjuntos

Si hemos elegido una organización "Asociativa por conjuntos" usaremos este cuadro para definir el número de vías, es decir, el número de bloques de los que consta cada conjunto.

## D.5. Asistente > Configurar > Página 3. Caché de nivel 3. Reemplazamiento

A través de este cuadro fijamos la política de reemplazamiento de este nivel de memoria.

Debemos tener en cuenta que la política de reemplazamiento no influye si elegimos una organización por Mapeado Directo.

Y que si elegimos una organización Asociativa por conjuntos sólo tiene influencia sobre el conjunto que corresponde al nuevo bloque

Podemos elegir entre:

## • AZAR

Cuando la memoria caché se encuentra llena el bloque a reemplazar es elegido al azar.

## • FIFO (First In - First Out)

Se reemplaza aquel bloque que lleva más tiempo en memoria.

Se implementa usando un contador de 0 a Num bloques, de manera que los nuevos bloques entran a 0, aumentando el contador en 1 del resto de los

bloques. Así el bloque con el contador más alto es el que lleva más tiempo en memoria, por lo que es el elegido para ser reemplazado.

• LRU (Least Recently Used) - Menos recientemente usada

Se reemplaza aquel bloque que lleva más tiempo en memoria sin ser usado.

Se implementa usando un contador de 0 a Num bloques, de manera que los nuevos bloques entran a 0, aumentando el contador en 1 del resto de los bloques.

Además cuando un bloque es referenciado su contador se pone de nuevo a 0 y se incrementan en 1 aquellos contadores que sean menores. Así el bloque con el contador más alto es el que lleva más tiempo en memoria sin ser usado, por lo que es el elegido para ser reemplazado.

## • CLOCK aproximación a LRU

Se reemplaza aquel bloque que lleva más tiempo en memoria sin ser usado.

Se implementa sin necesidad de contador, tan sólo se necesita un puntero que determina la posición siguiente a ser reemplazada. La posición actual de este puntero se muestra en un recuadro bajo la memoria.

El puntero avanza una posición, y si esa posición tiene el bit de modificado a 1, indicando que ha sido modificada recientemente, lo pone a 0 y avanza a la siguiente posición. Si tiene el bit a 0 esa es el bloque elegido para ser reemplazado.

• LFU (Least Frequently Used) - Menos frecuentemente usada

Se reemplaza aquel bloque que ha sido usado un menor número de veces.

Se implementa utilizando un contador que se inicializa a 0 cuando el bloque entra en memoria y se incrementa en 1 cada vez que el bloque es referenciado.

• NUR (Not Used Recently) - No recientemente usada

Se reemplaza aquel bloque que no ha sido usado recientemente.

Para determinar esta situación se basa en dos factores: si el bloque ha sido referenciado y si el bloque ha sido modificado. Dando lugar a cuatro posibles situaciones:

- 00 (0) Página no referenciada y no modificada

- 01 (1) Página no referenciada pero modificada

- 10 (2) Página referenciada pero no modificada

• 11 (3) - Página referenciada y modificada

Para implementarlo se utiliza un contador que se inicializa a 0 cuando el bloque entra en memoria por un acceso a instrucciones FETCH o una lectura de memoria MEMREAD, y a 1 si entra por una escritura en memoria MEMWRITE. Posteriormente, si el bloque es referenciado pasa de 0 a 2 o de 1 a 3, y si es modificado, de 2 a 3. Así el bloque elegido para ser reemplazado es el que tiene el contador más bajo.

# D.6. Asistente > Configurar > Página 3. Caché de nivel 3. Memoria

A través de este cuadro fijamos los parámetros de la memoria caché de nivel 3:

- TAMAÑO (en Kbytes): Tamaño físico de la memoria caché de este nivel.

- TIEMPO DE ACCESO (en ciclos): Tiempo empleado para acceder a una página situada en este nivel de caché.

# D.7. Asistente > Configurar > Página 3. Caché de nivel 3. Bus

A través de este cuadro fijamos los parámetros del bus entre la memoria caché de nivel 3 y la memoria principal:

- ANCHO (en bits): Ancho del bus situado entre memoria caché de nivel 3 y memoria principal.

- TIEMPO DE ACCESO (en ciclos): Tiempo empleado para trasladar una palabra entre la memoria caché de nivel 3 y la memoria principal a través de este bus.

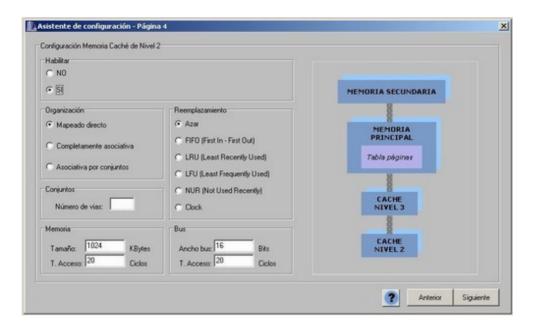

## E. Asistente > Configurar > Página 4

A través de esta ventana podemos configurar los siguientes parámetros de la caché de nivel 2:

- Habilitar o deshabilitar este nivel de memoria.

- Definir la organización.

- Establecer el número de conjuntos.

- Establecer la política de reemplazamiento.

- Definir los parámetros de la memoria.

- Definir los parámetros del bus.

Captura 5.8. Asistente de configuración – Página 4

## E.1. Asistente > Configurar > Página 4. Caché de nivel 2. Habilitar

A través de este cuadro habilitamos o deshabilitamos el uso de la memoria caché de nivel 2.

Si deshabilitamos la memoria caché de este nivel el resto de los parámetros de la página dejan de estar disponibles pues pierden su significado.

## E.2. Asistente > Configurar > Página 4. Caché de nivel 2. Organización

A través de este cuadro fijamos la organización de este nivel de memoria.

Podemos elegir entre:

#### MAPEADO DIRECTO

Cada bloque tiene un sólo lugar donde ser colocado en memoria caché según la fórmula

(Página de memoria principal) MOD (Número de bloques en caché)

## • COMPLETAMENTE ASOCIATIVA

Cada bloque puede ser colocado en cualquier lugar de la memoria caché.

## • ASOCIATIVA POR CONJUNTOS

A cada bloque le corresponde un conjunto dentro de memoria caché, de manera que puede ser colocada en cualquier posición dentro del conjunto, según la formula:

(Bloque de memoria caché) MOD (Número de conjuntos en caché)

Si un conjunto tiene n bloques se denomina Memoria Asociativa por Conjuntos de N-Vias.

## E.3. Asistente > Configurar > Página 4. Caché de nivel 2. Número de conjuntos

Si hemos elegido una organización "Asociativa por conjuntos" usaremos este cuadro para definir el número de vías, es decir, el número de bloques de los que consta cada conjunto.

# E.4. Asistente > Configurar > Página 4. Caché de nivel 2. Reemplazamiento

A través de este cuadro fijamos la política de reemplazamiento de este nivel de memoria.

Debemos tener en cuenta que la política de reemplazamiento no influye si elegimos una organización por Mapeado Directo.

Y que si elegimos una organización Asociativa por conjuntos sólo tiene influencia sobre el conjunto que corresponde al nuevo bloque

## Podemos elegir entre:

## • AZAR

Cuando la memoria caché se encuentra llena el bloque a reemplazar es elegido al azar.

## • FIFO (First In - First Out)

Se reemplaza aquel bloque que lleva más tiempo en memoria.

Se implementa usando un contador de 0 a Num bloques, de manera que los nuevos bloques entran a 0, aumentando el contador en 1 del resto de los bloques. Así el bloque con el contador más alto es el que lleva más tiempo en memoria, por lo que es el elegido para ser reemplazado.

## • LRU (Less Recently Used) - Menos recientemente usada

Se reemplaza aquel bloque que lleva más tiempo en memoria sin ser usado.

Se implementa usando un contador de 0 a Num bloques, de manera que los nuevos bloques entran a 0, aumentando el contador en 1 del resto de

los bloques. Además cuando un bloque es referenciado su contador se pone de nuevo a 0 y se incrementan en 1 aquellos contadores que sean menores. Así el bloque con el contador más alto es el que lleva más tiempo en memoria sin ser usado, por lo que es el elegido para ser reemplazado.

# • CLOCK aproximación a LRU

Se reemplaza aquel bloque que lleva más tiempo en memoria sin ser usado.

Se implementa sin necesidad de contador, tan sólo se necesita un puntero que determina la posición siguiente a ser reemplazada. La posición actual de este puntero se muestra en un recuadro bajo la memoria.

El puntero avanza una posición, y si esa posición tiene el bit de modificado a 1, indicando que ha sido modificada recientemente, lo pone a 0 y avanza a la siguiente posición. Si tiene el bit a 0 esa es el bloque elegido para ser reemplazado.

## • LFU (Least Frequently Used) - Menos frecuentemente usada

Se reemplaza aquel bloque que ha sido usado un menor número de veces. Se implementa utilizando un contador que se inicializa a 0 cuando el bloque entra en memoria y se incrementa en 1 cada vez que el bloque es referenciado.

• NUR (Not Used Recently) - No recientemente usada

Se reemplaza aquel bloque que no ha sido usado recientemente.

Para determinar esta situación se basa en dos factores: si el bloque ha sido referenciado y si el bloque ha sido modificado. Dando lugar a cuatro posibles situaciones:

- 00 (0) Página no referenciada y no modificada

- 01 (1) Página no referenciada pero modificada

- 10 (2) Página referenciada pero no modificada

- 11 (3) Página referenciada y modificada

Para implementarlo se utiliza un contador que se inicializa a 0 cuando el bloque entra en memoria por un acceso a instrucciones FETCH o una lectura de memoria MEMREAD, y a 1 si entra por una escritura en memoria MEMWRITE. Posteriormente, si el bloque es referenciado pasa

de 0 a 2 o de 1 a 3, y si es modificado, de 2 a 3. Así el bloque elegido para ser reemplazado es el que tiene el contador más bajo.

# E.5. Asistente > Configurar > Página 4. Caché de nivel 2. Memoria

A través de este cuadro fijamos los parámetros de la memoria caché de nivel 2:

- TAMAÑO (en Kbytes): Tamaño físico de la memoria caché de este nivel.

- TIEMPO DE ACCESO (en ciclos): Tiempo empleado para acceder a una página situada en este nivel de caché.

# E.6. Asistente > Configurar > Página 4. Caché de nivel 2. Bus

A través de este cuadro fijamos los parámetros del bus entre la memoria caché de nivel 3 y la caché de nivel 2, o bien entre la caché de nivel 2 y la memoria principal:

- ANCHO (en bits): Ancho del bus situado entre memoria caché de nivel 3 y la caché de nivel 2, o bien entre la caché de nivel 2 y la memoria principal.

- TIEMPO DE ACCESO (en ciclos): Tiempo empleado para trasladar una palabra entre la memoria caché de nivel 3 y la caché de nivel 2, o bien entre la caché de nivel 2 y la memoria principal a través de este bus.

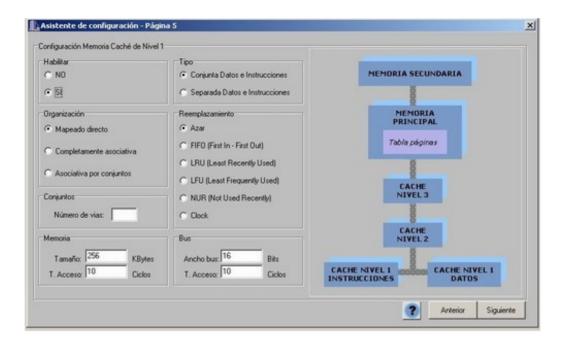

## F. Asistente > Configurar > Página 5

A través de esta ventana podemos configurar los siguientes parámetros de la caché de nivel 1:

- Habilitar o deshabilitar este nivel de memoria.

- Definir el tipo.

- Definir la organización.

- Establecer el número de conjuntos.

- Establecer la política de reemplazamiento.

- Definir los parámetros de la memoria.

- Definir los parámetros del bus.

Captura 5.9. Asistente de configuración – Página 5

## F.1. Asistente > Configurar > Página 5. Caché de nivel 1. Habilitar

A través de este cuadro habilitamos o deshabilitamos el uso de la memoria caché de nivel 1.

Si deshabilitamos la memoria caché de este nivel el resto de los parámetros de la página dejan de estar disponibles pues pierden su significado.

## F.2. Asistente > Configurar > Página 5. Caché de nivel 1. Tipo

A través de este cuadro definimos el tipo de memoria caché de nivel 1.

Podemos elegir entre:

## • CONJUNTA

Datos e Instrucciones comparten la misma memoria.

## • SEPARADA

Datos e Instrucciones utilizan memorias separadas.

# F.3. Asistente > Configurar > Página 5. Caché de nivel 1. Organización

A través de este cuadro fijamos la organización de este nivel de memoria.

Podemos elegir entre:

#### MAPEADO DIRECTO

Cada bloque tiene un sólo lugar donde ser colocado en memoria caché según la fórmula

(Página de memoria principal) MOD (Número de bloques en caché)

## • COMPLETAMENTE ASOCIATIVA

Cada bloque puede ser colocado en cualquier lugar de la memoria caché.

## • ASOCIATIVA POR CONJUNTOS

A cada bloque le corresponde un conjunto dentro de memoria caché, de manera que puede ser colocada en cualquier posición dentro del conjunto, según la formula:

(Bloque de memoria caché) MOD (Número de conjuntos en caché)

Si un conjunto tiene n bloques se denomina Memoria Asociativa por Conjuntos de N-Vías.

## F.4. Asistente > Configurar > Página 5. Caché de nivel 1. Número de conjuntos

Si hemos elegido una organización "Asociativa por conjuntos" usaremos este cuadro para definir el número de vías, es decir, el número de bloques de los que consta cada conjunto.

## F.5. Asistente > Configurar > Página 5. Caché de nivel 1. Reemplazamiento

A través de este cuadro fijamos la política de reemplazamiento de este nivel de memoria.

Debemos tener en cuenta que la política de reemplazamiento no influye si elegimos una organización por Mapeado Directo y que si elegimos una organización Asociativa por conjuntos, sólo tiene influencia sobre el conjunto que corresponde al nuevo bloque.

Podemos elegir entre:

#### • AZAR

Cuando la memoria caché se encuentra llena el bloque a reemplazar es elegido al azar.

## • FIFO (First In - First Out)

Se reemplaza aquel bloque que lleva más tiempo en memoria.

Se implementa usando un contador de 0 a Num bloques, de manera que los nuevos bloques entran a 0, aumentando el contador en 1 del resto de los bloques. Así el bloque con el contador más alto es el que lleva más tiempo en memoria, por lo que es el elegido para ser reemplazado.

## • LRU (Least Recently Used) - Menos recientemente usada

Se reemplaza aquel bloque que lleva más tiempo en memoria sin ser usado.

Se implementa usando un contador de 0 a Num bloques, de manera que los nuevos bloques entran a 0, aumentando el contador en 1 del resto de los bloques. Además cuando un bloque es referenciado su contador se pone de nuevo a 0 y se incrementan en 1 aquellos contadores que sean menores. Así el bloque con el contador más alto es el que lleva más tiempo en memoria sin ser usado, por lo que es el elegido para ser reemplazado.

## • CLOCK aproximación a LRU

Se reemplaza aquel bloque que lleva más tiempo en memoria sin ser usado.

Se implementa sin necesidad de contador, tan sólo se necesita un puntero que determina la posición siguiente a ser reemplazada. La posición actual de este puntero se muestra en un recuadro bajo la memoria.

El puntero avanza una posición, y si esa posición tiene el bit de modificado a 1, indicando que ha sido modificada recientemente, lo pone a 0 y avanza a la siguiente posición. Si tiene el bit a 0 esa es el bloque elegido para ser reemplazado.

## • LFU (Least Frequently Used) - Menos frecuentemente usada

Se reemplaza aquel bloque que ha sido usado un menor número de veces.

Se implementa utilizando un contador que se inicializa a 0 cuando el bloque entra en memoria y se incrementa en 1 cada vez que el bloque es referenciado.

• NUR (Not Used Recently) - No recientemente usada Se reemplaza aquel bloque que no ha sido usado recientemente.

Para determinar esta situación se basa en dos factores: si el bloque ha sido referenciado y si el bloque ha sido modificado. Dando lugar a cuatro posibles situaciones:

- 00 (0) Página no referenciada y no modificada

- 01 (1) Página no referenciada pero modificada

- 10 (2) Página referenciada pero no modificada

- 11 (3) Página referenciada y modificada

Para implementarlo se utiliza un contador que se inicializa a 0 cuando el bloque entra en memoria por un acceso a instrucciones FETCH o una lectura de memoria MEMREAD, y a 1 si entra por una escritura en memoria MEMWRITE. Posteriormente, si el bloque es referenciado pasa de 0 a 2 o de 1 a 3, y si es modificado, de 2 a 3. Así el bloque elegido para ser reemplazado es el que tiene el contador más bajo.

## F.6. Asistente > Configurar > Página 5. Caché de nivel 1. Memoria

A través de este cuadro fijamos los parámetros de la memoria caché de nivel 1:

- TAMAÑO (en Kbytes): Tamaño físico de la memoria caché de este nivel.

- TIEMPO DE ACCESO (en ciclos): Tiempo empleado para acceder a una página situada en este nivel de caché.

## F.7. Asistente > Configurar > Página 5. Caché de nivel 1. Bus

A través de este cuadro fijamos los parámetros del bus entre la memoria caché de nivel 2 y la caché de nivel 1, o bien entre la caché de nivel 1 y la memoria principal:

- ANCHO (en bits): Ancho del bus situado entre memoria caché de nivel 2 y la caché de nivel 1, o bien entre la caché de nivel 1 y la memoria principal.

- TIEMPO DE ACCESO (en ciclos): Tiempo empleado para trasladar una palabra entre la memoria caché de nivel 2 y la caché de nivel 1, o bien entre la caché de nivel 1 y la memoria principal a través de este bus.

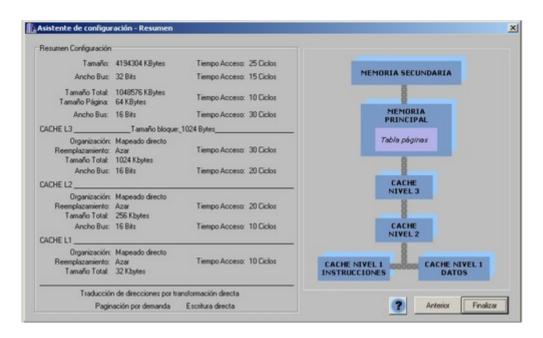

## G. Asistente > Configurar > Resumen

En esta ventana se muestran los parámetros elegidos durante la configuración del sistema, para que el usuario pueda validarlos, o bien volver atrás a corregir aquellos que haya introducido de forma incorrecta.

Captura 5.10. Asistente de configuración – Resumen

Al hacer clic sobre el botón "Siguiente" pasamos a la siguiente fase del proceso de simulación, la carga de un fichero de traza de un programa.

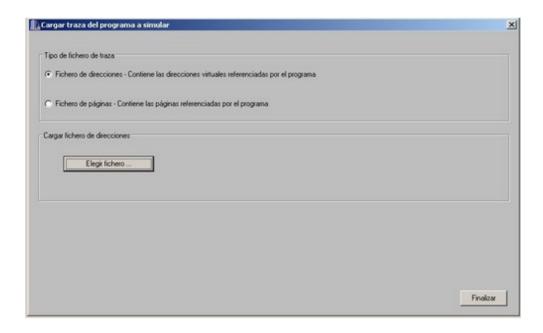

## 5.2.2.2. Asistente > Cargar programa

A través de esta ventana podemos elegir el fichero de traza sobre el que vamos a realizar la simulación.

Existen dos posibles tipos de ficheros a cargar:

• Fichero de direcciones (extensión .trd)

Contiene las direcciones virtuales referenciadas por un programa, real o simulado.

Si elegimos este tipo de fichero podremos visualizar luego la traducción de direcciones o la búsqueda de páginas.

• Fichero de páginas (extensión .trp)

Contiene las páginas referenciadas por un programa, real o simulado.

Si elegimos este tipo de fichero podremos visualizar sólo la búsqueda de páginas.

La estructura de estos ficheros se define en la sección Ficheros.

Al pulsar sobre el botón configurar del asistente se nos muestra la siguiente ventana:

Captura 5.11. Asistente – Cargar programa

Si el fichero de traza ya se encuentra cargado se muestra la ruta en el cuadro inferior.

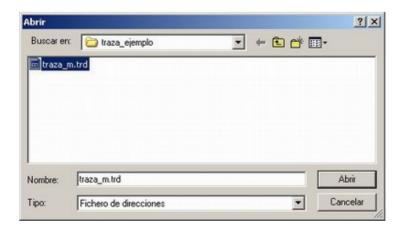

Elegimos el tipo de fichero de traza a cargar y pulsando sobre el botón "Elegir fichero" se nos muestra el cuadro de diálogo para acceder al fichero que deseamos cargar

Captura 5.12. Abrir fichero de traza

pulsamos sobre el botón abrir y una vez cargado el fichero se nos muestra la ruta del mismo en el cuadro inferior.

A continuación podemos pasar al siguiente paso del asistente pulsando el botón "Finalizar".

## 5.2.2.3. Asistente > Simular

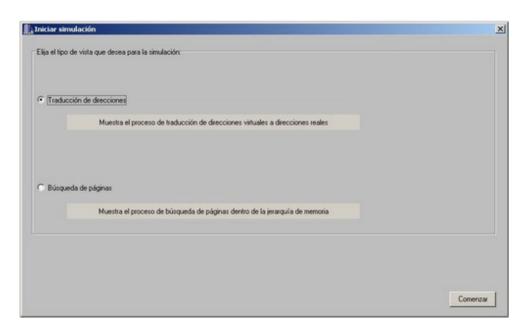

A través de esta ventana podemos elegir el tipo de simulación que deseamos realizar escogiendo entre las dos opciones:

## • Traducción de direcciones

Muestra el proceso de traducción de direcciones virtuales a direcciones reales.

# • Búsqueda de páginas

Muestra el proceso de búsqueda de páginas dentro de la jerarquía de memoria.

Captura 5.13 Asistente – Simular

y pulsando sobre el botón Comenzar.

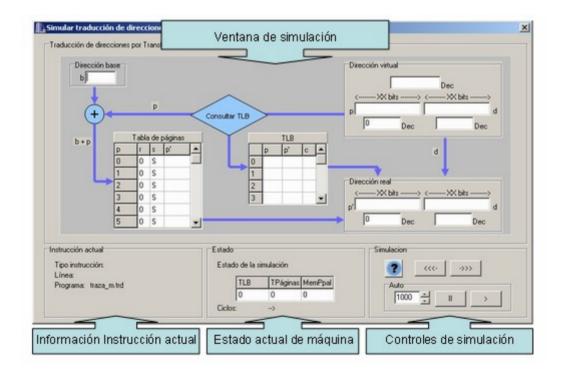

## 5.2.2.3.1. Traducción de direcciones

Muestra el proceso de traducción de direcciones virtuales a direcciones reales.

Según el método de traducción que hayamos elegido durante la configuración se nos muestran una de las siguientes ventanas:

- Simular traducción de direcciones por transformación directa.

- Simular traducción de direcciones por transformación asociativa-directa con 1 TLB.

- Simular traducción de direcciones por transformación asociativa-directa con 2 TLB.

## A.1. Simular traducción de direcciones por transformación directa

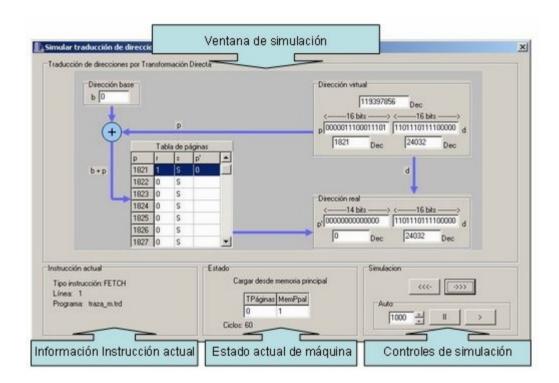

Al iniciar la traducción de direcciones por transformación directa el programa le muestra la siguiente ventana.

Captura 5.14 Simular traducción de direcciones por transformación directa

La ventana está dividida en 4 secciones:

- Ventana de simulación

- Información de la instrucción actual

- Estado actual de la máquina

- Controles de simulación

## A.1. Ventana de simulación

La ventana de simulación muestra gráficamente los pasos de cada instante de la simulación.

Se compone de:

## Dirección base

Dirección base de la tabla de páginas.

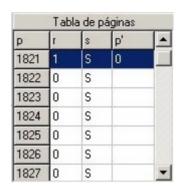

Captura 5.15. Tabla de páginas

Tabla de páginas que se compone de:

- p: Página dentro de la tabla de páginas.

- r: Bit de residencia, indica si la página se encuentra cargada en la tabla de páginas.

- s: Dirección de la página en memoria secundaria,

- p': Página en memoria principal.

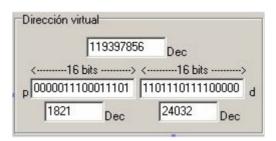

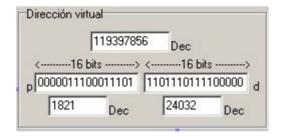

- Dirección virtual

Captura 5.16. Dirección virtual

Dirección de la instrucción en la memoria secundaria.

Dentro del cuadro se muestran:

- Dirección virtual en decimal.

- p: Página dentro de la tabla de páginas, en binario y en decimal.

- Número de bits de p.

- d: Desplazamiento dentro de la página, en binario y en decimal.

- Número de bits de d.

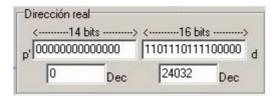

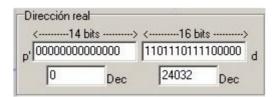

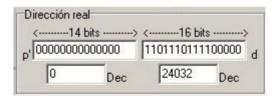

## • Dirección real

Captura 5.17. Dirección real

Dirección de la instrucción en la memoria principal

Dentro del cuadro se muestran:

- p': Página en memoria principal, en binario y en decimal.

- Número de bits de p'.

- d: Desplazamiento dentro de la página, en binario y en decimal.

- Número de bits de d.

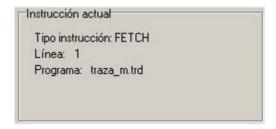

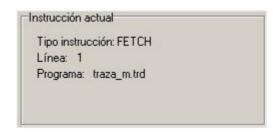

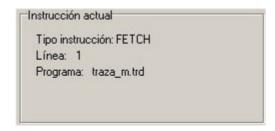

## A.2. Información de la instrucción actual

Muestra la siguiente información:

Captura 5.18. Información de la instrucción actual

• Tipo de acceso:

Tipo de acceso que se está tratando en ese instante.

- FETCH Búsqueda de instrucciones.

- MEMREAD Lectura de memoria.

- MEMWRITE Escritura en memoria.

- Línea

Línea de la traza que se está ejecutando en ese instante.

• Programa

Fichero de traza del programa que se está ejecutando en ese instante

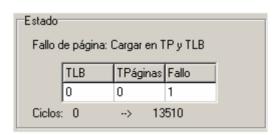

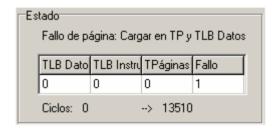

## A.3. Estado actual de la máquina

Muestra la siguiente información:

Captura 5.19. Estado actual de la máquina

#### • Estado:

Estado del simulador en ese instante:

- Fallo de página: Cargar en TP (Tabla de páginas): Debe cargar la página desde memoria secundaria a memoria principal y apuntar en la tabla de páginas.

- Acierto en tabla de páginas La página buscada se encuentra ya en memoria principal y apuntada en la tabla de páginas.

- Reemplazamiento en memoria principal La página a cargar desde memoria secundaria no cabe en memoria principal y es necesario reemplazar una de las páginas y actualizar la tabla de páginas.

#### • Estadística

Tabla que contiene el número de aciertos/fallos:

- Fallo Número de fallos, es decir, número de veces que la página ha tenido que ser cargada en memoria principal desde memoria secundaria y apuntada en la tabla de páginas.

- Acierto Número de veces que la página se ha encontrado en memoria principal.

## • Ciclos

Número de ciclos de CPU de la etapa anterior frente a número de ciclos de CPU consumidos en la etapa actual.

## A.4. Control de la simulación

Controla la ejecución de la simulación de dos formas:

Captura 5.20. Control de la simulación

## • Manual:

Control manual de la simulación

- Botón adelante (->>>) Realiza un paso hacia delante en la simulación.

- Botón atrás (<<<-) Realiza un paso hacia delante en la simulación.

#### Automático

Control automático de la simulación

- Botón adelante (>)- Realiza pasos hacia delante en la simulación cada "intervalo" elegido.

- Botón pausa (II) Pausa la simulación automática. Intervalo Intervalo de tiempo que transcurre entre los pasos.

- Intervalo: Intervalo de tiempo entre pasos. Usar las flechas abajo y arriba para decrementar o incrementar el intervalo.

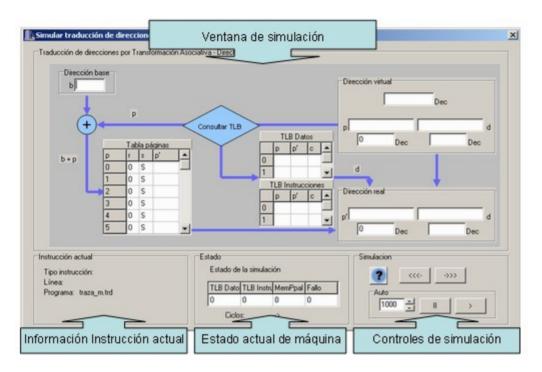

# B. Simular traducción de direcciones por transformación asociativa-directa con TLB

Al iniciar la traducción de direcciones por transformación directa el programa le muestra la siguiente ventana.

Captura 5.21. Traducción de direcciones por transformación asociativa-directa con TLB

La ventana está dividida en 4 secciones:

- Ventana de simulación

- Información de la instrucción actual

- Estado actual de la máquina

- Controles de simulación

## B.1. Ventana de simulación

La ventana de simulación muestra gráficamente los pasos de cada instante de la simulación. Se compone de:

• Dirección base

Dirección base de la tabla de páginas.

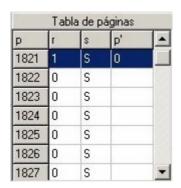

| Tabla de páginas |   |   |    |    |

|------------------|---|---|----|----|

| Р                | r | s | p' | •  |

| 1821             | 1 | S | 0  |    |

| 1822             | 0 | S |    |    |

| 1823             | 0 | S |    |    |

| 1824             | 0 | S |    |    |

| 1825             | 0 | S |    |    |

| 1826             | 0 | S |    | l, |

| 1827             | 0 | S |    |    |

Captura 5.22. Tabla de páginas

Tabla de páginas que se compone de:

- p: Página dentro de la tabla de páginas.

- r: Bit de residencia, indica si la página se encuentra cargada en la tabla de páginas.

- s: Dirección de la página en memoria secundaria,

- p': Página en memoria principal.

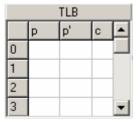

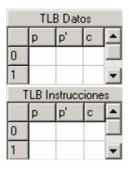

- TLB (Translation Lookaside buffer)

Captura 5.23. TLB

# Se compone de:

- *n*: Número de entrada en la TLB.

- p: Página dentro de la tabla de páginas.

- p': Página en memoria principal.

- c: Contador para la política de reemplazamiento.

Implementa una política de reemplazamiento FIFO.

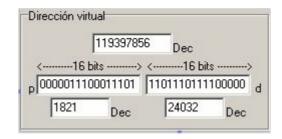

• Dirección virtual

Captura 5.24. Dirección virtual

Dirección de la instrucción en la memoria secundaria. Dentro del cuadro se muestran:

- Dirección virtual en decimal.

- p: Página dentro de la tabla de páginas, en binario y en decimal.

- Número de bits de p.

- d: Desplazamiento dentro de la página, en binario y en decimal.

- Número de bits de d.

- Dirección real

Captura 5.25. Dirección real

Dirección de la instrucción en la memoria principal

Dentro del cuadro se muestran:

- p': Página en memoria principal, en binario y en decimal.

- Número de bits de p'.

- d: Desplazamiento dentro de la página, en binario y en decimal.

- Número de bits de d.

## B.2. Información de la instrucción actual

Muestra la siguiente información:

Captura 5.26. Información de la instrucción actual

## • Tipo de acceso:

Tipo de acceso que se está tratando en ese instante.

- FETCH Búsqueda de instrucciones.

- MEMREAD Lectura de memoria.

- MEMWRITE Escritura en memoria.

#### • Línea

Línea de la traza que se está ejecutando en ese instante.

## • Programa

Fichero de traza del programa que se está ejecutando en ese instante

## B.3. Estado actual de la máquina

Muestra la siguiente información:

Captura 5.27. Estado actual de la máquina

#### • Estado:

Estado del simulador en ese instante:

- Fallo de página: Cargar en TP (Tabla de páginas) y TLB Debe cargar la página desde memoria secundaria a memoria principal y apuntar tanto en la tabla de páginas como en la TLB.

- Acierto en TLB La página buscada se encuentra ya en memoria principal y apuntada en la TLB y en la tabla de páginas.

- Acierto en tabla de páginas y cargar en TLB La página buscada se encuentra ya en memoria principal y apuntada en la tabla de páginas pero no en la TLB, por lo que se actualiza la TLB.

- Reemplazamiento en memoria principal La página a cargar desde memoria secundaria no cabe en memoria principal y es necesario reemplazar una de las páginas y actualizar tanto la tabla de páginas como la TLB.

#### • Estadística

Tabla que contiene el número de aciertos/fallos:

- Fallo Número de fallos, es decir, número de veces que la página ha tenido que ser cargada en memoria principal desde memoria secundaria y apuntada en la tabla de páginas.

- TPáginas Número de veces que la página se ha encontrado en memoria principal usando la tabla de páginas.

- TLB Número de veces que la página se ha encontrado en memoria principal usando la TLB.

#### • Ciclos

Número de ciclos de CPU de la etapa anterior frente a número de ciclos de CPU consumidos en la etapa actual.

## B.4. Control de la simulación

Controla la ejecución de la simulación de dos formas:

Captura 5.28. Control de la simulación

## • Manual:

Control manual de la simulación

- Botón adelante (->>>) Realiza un paso hacia delante en la simulación.

- Botón atrás (<<<-) Realiza un paso hacia delante en la simulación.

## • Automático

Control automático de la simulación

• Botón adelante (>)- Realiza pasos hacia delante en la simulación cada "intervalo" elegido.

- Botón pausa (II) Pausa la simulación automática. Intervalo Intervalo de tiempo que transcurre entre los pasos.

- Intervalo: Intervalo de tiempo entre pasos. Usar las flechas abajo y arriba para decrementar o incrementar el intervalo.

# C. Simular traducción de direcciones por transformación asociativa-directa con 2 TLB

Al iniciar la traducción de direcciones por transformación directa el programa le muestra la siguiente ventana.

Captura 5.29. Traducción de direcciones por transformación asociativa-directa con TLB dividida

La ventana está dividida en 4 secciones:

- Ventana de simulación

- Información de la instrucción actual

- Estado actual de la máquina

- Controles de simulación

## C.1. Ventana de simulación

La ventana de simulación muestra gráficamente los pasos de cada instante de la simulación. Se compone de:

• Dirección base

Dirección base de la tabla de páginas.

Captura 5.30. Tabla de páginas

Tabla de páginas que se compone de:

- p: Página dentro de la tabla de páginas.

- r: Bit de residencia, indica si la página se encuentra cargada en la tabla de páginas.

- s: Dirección de la página en memoria secundaria,

- p': Página en memoria principal.

- TLB (Translation Lookaside buffer)

Se divide en TLB de datos y TLB de instrucciones.

Captura 5.31. TLB Dividida

Cada una de las divisiones se compone de:

- *n*: Número de entrada en la TLB.

- p: Página dentro de la tabla de páginas.

- p': Página en memoria principal.

- c: Contador para la política de reemplazamiento.

Implementa una política de reemplazamiento FIFO.

• Dirección virtual

Captura 5.32. Dirección virtual

Dirección de la instrucción en la memoria secundaria. Dentro del cuadro se muestran:

- Dirección virtual en decimal.

- p: Página dentro de la tabla de páginas, en binario y en decimal.

- Número de bits de p.

- d: Desplazamiento dentro de la página, en binario y en decimal.

- Número de bits de d.

- Dirección real

Captura 5.33. Dirección real

Dirección de la instrucción en la memoria principal. Dentro del cuadro se muestran:

- p': Página en memoria principal, en binario y en decimal.

- Número de bits de p'.

- d: Desplazamiento dentro de la página, en binario y en decimal.

- Número de bits de d.

## C.2. Información de la instrucción actual

Muestra la siguiente información:

Captura 5.34. Información de la instrucción actual

## • Tipo de acceso:

Tipo de acceso que se está tratando en ese instante.

- FETCH Búsqueda de instrucciones.

- MEMREAD Lectura de memoria.

- MEMWRITE Escritura en memoria.

#### • Línea:

Línea de la traza que se está ejecutando en ese instante.

## • Programa:

Fichero de traza del programa que se está ejecutando en ese instante

## C.3. Estado actual de la máquina

Muestra la siguiente información:

Captura 5.35. Estado actual de la máquina

## • Estado:

Estado del simulador en ese instante:

- Fallo de página: Cargar en TP (Tabla de páginas) y TLB (Datos o Instrucciones) Debe cargar la página desde memoria secundaria a memoria principal y apuntar tanto en la tabla de páginas como en la TLB (Datos o Instrucciones).

- Acierto en TLB (Datos o Instrucciones) La página buscada se encuentra ya en memoria principal y apuntada en la TLB y en la tabla de páginas.

- Acierto en tabla de páginas y cargar en TLB (Datos o Instrucciones) La página buscada se encuentra ya en memoria principal y apuntada en la tabla de páginas pero no en la TLB, por lo que se actualiza la TLB (Datos o Instrucciones).

- Reemplazamiento en memoria principal La página a cargar desde memoria secundaria no cabe en memoria principal y es necesario reemplazar una de las páginas y actualizar tanto la tabla de páginas como la TLB (Datos o Instrucciones).

#### • Estadística

Tabla que contiene el número de aciertos/fallos:

- Fallo Número de fallos, es decir, número de veces que la página ha tenido que ser cargada en memoria principal desde memoria secundaria y apuntada en la tabla de páginas.

- TPáginas Número de veces que la página se ha encontrado en memoria principal usando la tabla de páginas.

TLB (Datos o Instrucciones) - Número de veces que la página se ha encontrado en memoria principal usando la TLB (Datos o Instrucciones).

#### • Ciclos

Número de ciclos de CPU de la etapa anterior frente a número de ciclos de CPU consumidos en la etapa actual.

#### C.4. Control de la simulación

Controla la ejecución de la simulación de dos formas:

Captura 5.36. Control de la simulación

## • Manual:

Control manual de la simulación

- Botón adelante (->>>) Realiza un paso hacia delante en la simulación.

- Botón atrás (<<<-) Realiza un paso hacia delante en la simulación.

#### • Automático

Control automático de la simulación

- Botón adelante (>)- Realiza pasos hacia delante en la simulación cada "intervalo" elegido.

- Botón pausa (II) Pausa la simulación automática. Intervalo Intervalo de tiempo que transcurre entre los pasos.

• Intervalo: Intervalo de tiempo entre pasos. Usar las flechas abajo y arriba para decrementar o incrementar el intervalo.

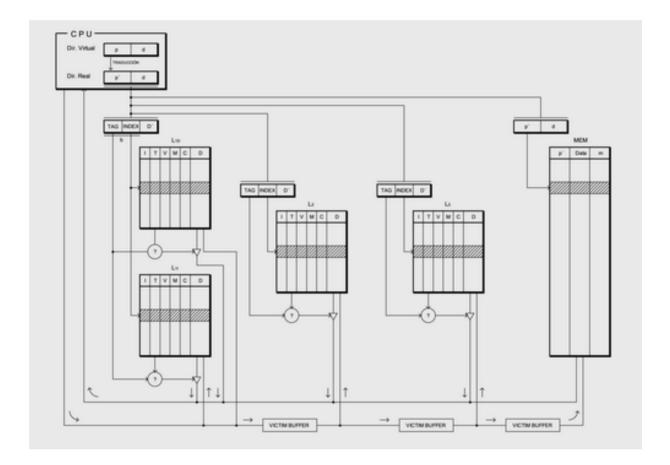

# 5.2.2.3.2. Simular búsqueda de direcciones en memoria

Muestra el proceso de búsqueda de direcciones dentro de la jerarquía de memoria. La máquina simulada sigue la siguiente estructura:

Figura 5.1. Estructura de la jerarquía de memoria implementada

NOTA: Los diferentes niveles de caché pueden o no estar activos, así como en escritura retardada el/los Victim Buffer/s no está/n presentes.

Al elegir esta opción se muestra la siguiente ventana que está dividida en 7 secciones:

- Memoria principal

- Memoria caché

- CPU

- Estado actual de la máquina

- Información de la instrucción actual

- Controles de simulación

Captura 5.37. Búsqueda de direcciones/páginas

## A. Memoria principal

Muestra la memoria principal. Se compone de:

- p': Página en memoria principal.

- p: Página dentro de la tabla de páginas.

- m: Bit de modificación, indica si la página se ha modificado mientras se encontraba cargada en memoria principal.

Captura 5.38. Memoria principal

La memoria principal implementa un algoritmo de reemplazamiento FIFO.

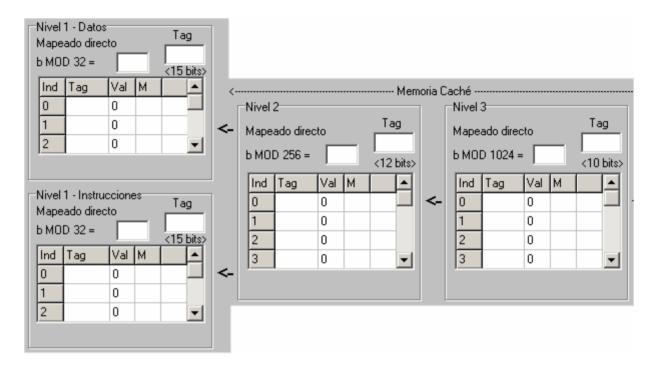

#### B. Memoria Caché

Muestra los diferentes niveles de caché según la configuración que hayamos elegido al configurar el simulador.

Captura 5.39. Memoria caché

Según la configuración elegida se nos mostrarán:

- Caché de nivel 3.

- Caché de nivel 2.

- Caché de nivel 1, bien conjunta o bien separada en Nivel 1 Datos y Nivel 1 Instrucciones.

Cada una de estos niveles se compone de:

- Organización elegida para ese nivel de caché.

- Cálculo de la posición del bloque en ese nivel de caché (sólo en "Mapeado directo" y "Asociativa por conjuntos").

- Tag: Etiqueta con el Tag buscado en ese instante en ese nivel de caché, así como su tamaño en bits.

- Política de reemplazamiento elegida para ese nivel de caché (no en "Mapeado directo").

- Contenido de ese nivel de caché:

- Ind (Index): Índice del bloque de memoria caché.

- Tag: Etiqueta del bloque de memoria caché.

- Val (Valid): Bit válido del bloque de memoria caché.

- M (Modified): Bit de modificación, indica si el bloque se ha modificado mientras se encontraba cargado en ese nivel de caché.

- C (Counter): Bit contador, bit utilizado para aplicar las diferentes políticas de reemplazamiento (no aparece si elegimos mapeado directo o política de reemplazamiento clock o al azar).

Cuando elegimos CLOCK como política de reemplazamiento se nos muestra un cuadro con el contador en ese instante.

#### C. CPU

Muestra la dirección física solicitada por la CPU una vez ha sido obtenida de la dirección virtual.

Captura 5.40. CPU

Se compone de:

- Dirección real en binario: Muestra la dirección real en binario solicitada por la CPU.

- Dirección real en decimal compuesta por:

- p': Página real.

- d: Desplazamiento dentro de la página.

Sobre ella se muestran los bits que componen cada una de las divisiones.

- Dirección caché en decimal compuesta por:

- b: Bloque.

- d': Desplazamiento dentro del bloque.

Sobre ella se muestran los bits que componen cada una de las divisiones.

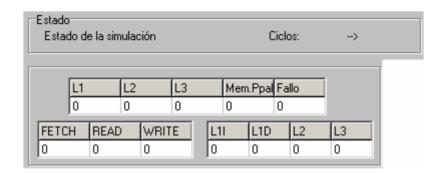

## D. Estado actual de la máquina

Muestra la siguiente información:

Captura 5.41. Estado actual de la máquina

#### • Estado:

Estado del simulador en ese instante

- Cargar desde memoria principal Debe cargar la instrucción/datos desde memoria secundaria a memoria principal y los diferentes niveles de cache.

- Acierto en memoria principal La instrucción/datos se encuentran cargados en memoria principal, y deben ser cargados a los diferentes niveles de cache.

- Acierto en caché de nivel X (de datos y/o de instrucciones) La instrucción/datos se encuentran cargados en el nivel X de caché y deben ser cargados a los niveles superiores.

#### • Ciclos:

Número de ciclos de CPU de la etapa anterior frente a número de ciclos de CPU consumidos en la etapa actual.

#### • Estadística

Tabla que contiene el número de aciertos/fallos

- L1 Número de veces que la instrucción se ha encontrado en la cache de nivel 1.

- L2 Número de veces que la instrucción se ha encontrado en la cache de nivel 2.

- L3 Número de veces que la instrucción se ha encontrado en la cache de nivel 3.

- MemPpal Número de veces que la instrucción se ha encontrado en memoria principal.

- Fallo Número de fallos, es decir, número de veces que la instrucción ha tenido que ser cargada en memoria principal.

Número de instrucciones de cada tipo:

- FETCH Búsqueda de instrucciones.

- MEMREAD Lectura de memoria.

- MEMWRITE Escritura en memoria.

Número de reemplazamientos:

- L1I Número de reemplazamientos en la caché de instrucciones de nivel 1.

- L1D Número de reemplazamientos en la caché de datos de nivel 1.

- L2 Número de reemplazamientos en la caché de instrucciones de nivel 2.

- L3 Número de reemplazamientos en la caché de instrucciones de nivel 3.

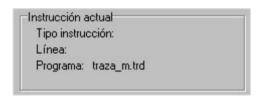

# E. Información de la instrucción actual

Muestra la siguiente información:

Captura 5.42. Información de la instrucción actual

• Tipo de acceso:

Tipo de acceso que se está tratando en ese instante.

- FETCH Búsqueda de instrucciones.

- MEMREAD Lectura de memoria.

- MEMWRITE Escritura en memoria.

- Línea

Línea de la traza que se está ejecutando en ese instante.

• Programa

Fichero de traza del programa que se está ejecutando en ese instante

#### F. Control de la simulación

Controla la ejecución de la simulación de dos formas:

Captura 5.43. Control de la simulación

#### • Manual:

Control manual de la simulación

- Botón adelante (->>>) Realiza un paso hacia delante en la simulación.

- Botón atrás (<<<-) Realiza un paso hacia delante en la simulación.

## Automático

Control automático de la simulación

- Botón adelante (>)- Realiza pasos hacia delante en la simulación cada "intervalo" elegido.

- Botón pausa (II) Pausa la simulación automática. Intervalo Intervalo de tiempo que transcurre entre los pasos.

- Intervalo: Intervalo de tiempo entre pasos. Usar las flechas abajo y arriba para decrementar o incrementar el intervalo.

# 5.2.3. Ficheros de SIJEM

- Tipos de ficheros

- Ficheros de ejemplo

## 5.2.3.1. Tipos de ficheros de SIJEM

Para la ejecución del simulador es necesario un fichero de traza, que puede ser de dos tipos:

- Fichero de direcciones (extensión .trd)

Contiene las direcciones virtuales referenciadas por un programa, real o simulado, según la siguiente estructura:

- DIRECCION: Contiene una dirección virtual de X bit que representa la dirección generada por el programa en ejecución.

- TIPO DE INSTRUCCIÓN: Indica el tipo de instrucción, que puede ser:

- FETCH Búsqueda de instrucciones.

- MEMREAD Lectura de memoria.

- MEMWRITE Escritura en memoria.

- TIEMPO: Indica el tiempo (Delta) transcurrido desde la última petición de página en ciclos de reloj.

- Fichero de páginas (extensión .trp)

Contiene las páginas referenciadas por un programa, real o simulado, según la siguiente estructura:

- PÁGINA: Contiene la página referenciada por el programa en ejecución.

- TIPO DE INSTRUCCIÓN: Indica el tipo de instrucción, que puede ser:

- FETCH Búsqueda de instrucciones.

- MEMREAD Lectura de memoria.

- MEMWRITE Escritura en memoria.

- DIRECCION: Contiene una dirección virtual de X bit que representa la dirección generada por el programa en ejecución. En caso de no conocerla puede ser 0 siempre.

Y opcionalmente podemos guardar todos los parámetros de configuración en otro fichero:

• Fichero de configuración (extensión .cfg)

Puede contener todos o algunos de los parámetros de configuración, según la estructura:

```

/Tamaño total de memoria secundaria (en Kbytes)

/Tiempo acceso a memoria secundaria (en ciclos)

/Ancho bus Memoria Secundaria-Memoria principal (en bits)

/Tiempo acceso bus Memoria Secundaria-Memoria principal (en ciclos)

/Tamaño total memoria principal (en Kbytes)

/Tamaño página (en Kbytes)

/Tiempo acceso memoria principal (en ciclos)

-7:

/Traducción direcciones

/(1 - Directa, 2 - Asociativa directa con 1 TLB, 3 - Asociativa directa con 2 TLB)

/Número de entradas de la TLB

/Tiempo de acceso a la TLB (en ciclos)

/Tipo de paginación 1

/(1 - Por demanda, 2 - Anticipada)

-11:

/Tipo de paginación 2

```

```

/(1 - Escritura directa, 2 - Escritura retardada)

-12:

/Caché habilitada

/(0 - NO. 1 - SI)

-13:

/Tamaño del bloque de caché (en bytes)

/Caché de nivel 3 habilitada?

/(0 - NO, 1 - SI)

-15:

/Organización de la cache de nivel 3

/(1 - Mapeado directo, 2 - Completamente asociativa, 3 - Asociativa por conjuntos)

-16:

/Política de reemplazamiento de cache de nivel 3

/(1 - AZAR, 2 - FIFO, 3 - LRU, 4 - LFU, 5 - NUR, 6 - CLOCK)

/Tamaño de la caché de nivel 3 (en Kbytes)

/Tiempo de acceso a la caché de nivel 3 (en Ciclos)

-19:

/Ancho bus memoria caché nivel 3 a nivel superior (en Bits)

/Tiempo acceso bus memoria caché nivel 3 a nivel superior (en Ciclos)

/Número de vías de la caché de nivel 3 (si es asociativa por conjuntos)

-22:

/Caché de nivel 2 habilitada?

/(0 - NO, 1 - SI)

-23:

/Organización de la cache de nivel 2

/(1 - Mapeado directo, 2 - Completamente asociativa, 3 - Asociativa por conjuntos)

-24:

/Política de reemplazamiento de cache de nivel 2

/(1 - AZAR, 2 - FIFO, 3 - LRU, 4 - LFU, 5 - NUR, 6 - CLOCK)

/Tamaño de la caché de nivel 2 (en Kbytes)

/Tiempo de acceso a la caché de nivel 2 (en Ciclos)

/Ancho bus memoria caché nivel 2 a nivel superior (en Bits)

/Tiempo acceso bus memoria caché nivel 2 a nivel superior (en Ciclos)

/Número de vías de la caché de nivel 2 (si es asociativa por conjuntos)

/Caché de nivel 1 habilitada?

/(0 - NO, 1 - SI)

-31:

/Tipo de caché de nivel 1

/(1 - Conjunta, 2 - Separada)

-32:

/Organización de la cache de nivel 1

/(1 - Mapeado directo, 2 - Completamente asociativa, 3 - Asociativa por conjuntos)

-33:

/Política de reemplazamiento de cache de nivel 1

/(1 - AZAR, 2 - FIFO, 3 - LRU, 4 - LFU, 5 - NUR, 6 - CLOCK)

/Tamaño de la caché de nivel 1 (en Kbytes)

```

-35:

/Tiempo de acceso a la caché de nivel 1 (en Ciclos)

-36:

/Ancho bus memoria caché nivel 1 a nivel superior (en Bits)

-37:

/Tiempo acceso bus memoria caché nivel 1 a nivel superior (en Ciclos)

-38:

/Número de vías de la caché de nivel 1 (si es asociativa por conjuntos)

-39:

Ejemplo 5.1. Ficheros de configuración

Para insertar comentarios se utiliza '/'.

# 5.2.3.2. Ficheros de ejemplo de SIJEM

En la carpeta "Ejemplos" del directorio donde hayamos instalado el simulador se proporcionan una serie de ejemplos para ejecutar pruebas:

- Fichero de configuración (extensión .cfg)

- Ficheros para el uso con traducción de direcciones

|                                                        | Ejem1.cfg                 | Ejem2.cfg                                       | Ejem3.cfg                                                |  |

|--------------------------------------------------------|---------------------------|-------------------------------------------------|----------------------------------------------------------|--|

| Tamaño total memoria secundaria                        | 1024 Kbytes               |                                                 |                                                          |  |

| Tiempo acceso memoria secundaria                       | 10000 ciclos              |                                                 |                                                          |  |

| Ancho bus memoria principal-<br>memoria secundaria     | 20 bits                   |                                                 |                                                          |  |

| Tiempo acceso bus memoria principal-memoria secundaria | 1500 ciclos               |                                                 |                                                          |  |

| Tamaño total memoria principal                         | 64 Kbytes                 |                                                 |                                                          |  |

| Tamaño página                                          | 4 Kbytes                  |                                                 |                                                          |  |

| Tiempo acceso memoria principal                        | 1000 ciclos               |                                                 |                                                          |  |

| Traducción de direcciones                              | Transformación<br>directa | Transformación<br>asociativa-directa<br>con TLB | Transformación<br>asociativa-directa<br>con TLB dividida |  |

| Carga de páginas                                       | Por demanda               |                                                 |                                                          |  |

| Coherencia                                             | Escritura directa         |                                                 |                                                          |  |

| Tamaño bloque caché                                    | 0 bytes                   |                                                 |                                                          |  |

| Caché nivel 3 habilitada                               | NO                        |                                                 |                                                          |  |

| Caché nivel 2 habilitada                               | NO                        |                                                 |                                                          |  |

| Caché nivel 1 habilitada                               | NO                        |                                                 |                                                          |  |

Tabla 5.1. Ficheros de configuración de ejemplo

# • Ficheros para el uso con búsqueda de direcciones

|                                  | Ejem4.cfg                                | Ejem5.cfg                | Ejem6.cfg | Ejem7.cfg |

|----------------------------------|------------------------------------------|--------------------------|-----------|-----------|

| Tamaño memoria secundaria        | 4194304 Kbytes (4Gbytes)                 |                          |           |           |

| T. acceso memoria secundaria     | 10000 ciclos                             |                          |           |           |

| Ancho bus memoria principal      | 32 bits                                  |                          |           |           |

| Tamaño total memoria principal   | 1500 ciclos                              |                          |           |           |

| Tamaño página                    | 4 Kbytes                                 |                          |           |           |

| T. acceso memoria principal      | 1000 ciclos                              |                          |           |           |

| Traducción de direcciones        | Transformación directa                   |                          |           |           |

| Carga de páginas                 | Por demanda                              |                          |           |           |

| Coherencia                       | Escritura directa                        |                          |           |           |

| Tamaño bloque caché              | 1024 Kbytes (1 Mbyte)                    |                          |           |           |

| Caché nivel 3 habilitada         | SI                                       |                          |           |           |

| Organización caché nivel 3       | Mapeado<br>directo                       | Completamente asociativa |           |           |

| Política reemplazamiento nivel 3 | -                                        | AZAR                     | FIFO      | LRU       |

| Tamaño caché nivel 3             | 16 Kbytes                                |                          |           |           |

| Tiempo acceso caché nivel 3      |                                          | 100 ciclos               |           |           |

| Ancho bus caché nivel 3          | 20 bits                                  |                          |           |           |

| Tiempo acceso bus caché nivel 3  | 50 ciclos                                |                          |           |           |

| Caché nivel 2 habilitada         | SI                                       |                          |           |           |

| Organización caché nivel 2       | Mapeado<br>directo                       |                          |           |           |

| Política reemplazamiento nivel 2 | -                                        | AZAR                     | FIFO      | LRU       |

| Tamaño caché nivel 2             | 8 Kbytes                                 |                          |           |           |

| Tiempo acceso caché nivel 2      | 50 ciclos                                |                          |           |           |

| Ancho bus caché nivel 2          | 14 bits                                  |                          |           |           |

| Tiempo acceso bus caché nivel 2  | 25 ciclos                                |                          |           |           |

| Caché nivel 1 habilitada         | SI                                       |                          |           |           |

| Tipo caché nivel 1               | Separada                                 |                          |           |           |

| Organización caché nivel 1       | Mapeado directo Completamente asociativa |                          |           |           |

| Política reemplazamiento nivel 1 | -                                        | AZAR                     | FIFO      | LRU       |

| Tamaño caché nivel 1             | 4 Kbytes (Datos) + 4 Kb (Instrucciones)  |                          |           |           |

| Tiempo acceso caché nivel 1      | 10 ciclos                                |                          |           |           |

| Ancho bus caché nivel 1          | 13 bits                                  |                          |           |           |

| Tiempo acceso bus caché nivel 1  | 5 ciclos                                 |                          |           |           |

Tabla 5.2. Ficheros de configuración de ejemplo

|                                  | Ejem8.cfg                               | Ejem9.cfg              | Ejem10.cfg                           | Ejem11.cfg |

|----------------------------------|-----------------------------------------|------------------------|--------------------------------------|------------|

| Tamaño memoria secundaria        | 4194304 Kbytes (4Gbytes)                |                        |                                      |            |

| T. acceso memoria secundaria     | 10000 ciclos                            |                        |                                      |            |

| Ancho bus memoria principal      | 32 bits                                 |                        |                                      |            |

| Tamaño total memoria principal   | 1500 ciclos                             |                        |                                      |            |

| Tamaño página                    | 4 Kbytes                                |                        |                                      |            |

| T. acceso memoria principal      | 1000 ciclos                             |                        |                                      |            |

| Traducción de direcciones        |                                         | Transformación directa |                                      |            |

| Carga de páginas                 |                                         | Por demanda            |                                      |            |

| Coherencia                       |                                         | Escritura directa      |                                      |            |

| Tamaño bloque caché              | 1024 Kbytes (1 Mbyte)                   |                        |                                      |            |

| Caché nivel 3 habilitada         |                                         |                        | SI                                   |            |

| Organización caché nivel 3       | Completamente asociativa                |                        | Asociativa por cjtos de 2 vías       |            |

| Política reemplazamiento nivel 3 | LFU                                     | NUR                    | CLOCK                                | AZAR       |

| Tamaño caché nivel 3             | 16 Kbytes                               |                        |                                      |            |

| Tiempo acceso caché nivel 3      | 100 ciclos                              |                        |                                      |            |

| Ancho bus caché nivel 3          | 20 bits                                 |                        |                                      |            |

| Tiempo acceso bus caché nivel 3  | 50 ciclos                               |                        |                                      |            |

| Caché nivel 2 habilitada         | SI                                      |                        |                                      |            |

| Organización caché nivel 2       | Completamente asociativa                |                        | Asociativa<br>por cjtos de 2<br>vías |            |

| Política reemplazamiento nivel 2 | LFU                                     | NUR                    | CLOCK                                | AZAR       |

| Tamaño caché nivel 2             |                                         | 8 I                    | Kbytes                               |            |

| Tiempo acceso caché nivel 2      |                                         | 50                     | ciclos                               |            |

| Ancho bus caché nivel 2          | 14 bits                                 |                        |                                      |            |

| Tiempo acceso bus caché nivel 2  | 25 ciclos                               |                        |                                      |            |

| Caché nivel 1 habilitada         | SI                                      |                        |                                      |            |

| Tipo caché nivel 1               | Separada                                |                        |                                      |            |

| Organización caché nivel 1       |                                         |                        | Asociativa por cjtos de 2 vías       |            |

| Política reemplazamiento nivel 1 | LFU                                     | NUR                    | CLOCK                                | AZAR       |

| Tamaño caché nivel 1             | 4 Kbytes (Datos) + 4 Kb (Instrucciones) |                        |                                      |            |

| Tiempo acceso caché nivel 1      | 10 ciclos                               |                        |                                      |            |

| Ancho bus caché nivel 1          | 13 bits                                 |                        |                                      |            |

| Tiempo acceso bus caché nivel 1  | 5 ciclos                                |                        |                                      |            |

Tabla 5.3. Ficheros de configuración de ejemplo

• Fichero de direcciones (extensión .trd)

Para las simulaciones se incluyen una serie de ficheros de traza de programas reales extraídos de ejecuciones del benchmark SPEC2000.

Su tipo se detalla en la siguiente tabla:

|          | Descripción                                   |  |

|----------|-----------------------------------------------|--|

| Crafty   | Programa de ajedrez                           |  |

| Eon_cook | Programa de trazado de rayos sobre una tetera |  |

| Facerec  | Programa de reconocimiento de caras           |  |

| Gcc      | Compilador de C y C++                         |  |

| Mesa     | Librería de gráficos 3D                       |  |

| Vortex   | Base de datos                                 |  |

Tabla 5.4. Ficheros de direcciones de ejemplo

Existen 5 ficheros de cada tipo, cada uno de ellos con un tipo de direcciones:

- Terminado en a: Direcciones de 32 bits (Ejemplos del 5 al 11) Memoria virtual hasta 4GB.

- Terminado en b: Direcciones de 28 bits Memoria virtual hasta 256MB.

- Terminado en c: Direcciones de 24 bits Memoria virtual hasta 16MB.

- Terminado en d: Direcciones de 20 bits (Ejemplos del 1 al 3) Memoria virtual hasta 1MB.

- Terminado en e: Direcciones de 16 bits Memoria virtual hasta 64kB.