# Estructura de Computadores

#### Tema 3. La unidad de memoria I. La memoria física

- Características y clasificación general de las memorias.

- Diseño de una unidad de memoria.

- Estructura interna de la memoria estática.

- Estructura interna de la memoria dinámica.

- Entrelazado.

- Memorias direccionables por contenido.

# 1. Ejercicios Resueltos

#### 1.1.

Dibujar los esquemas de:

- (a) una celda SRAM bipolar de dos transistores, y

- (b) una celda DRAM NMOS de un sólo transistor,

describiendo brevemente su funcionamiento, es decir, la forma en que queda almacenado un bit de información en ambos casos.

Trazar un cronograma de un ciclo de lectura para cada tipo de memoria: estática y dinámica. Resumir las ventajas y desventajas de la RAM dinámica frente a la RAM estática.

#### Solución

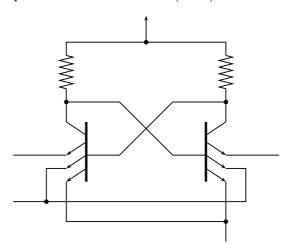

(a) La célula SRAM bipolar de dos transistores (TTL) es:

Esta célula consta de dos transistores acoplados en cruz, formando una báscula, en la que un transistor está en saturación y el otro al corte.

Supongamos que con  $T_1$  conduciendo y  $T_2$  al corte la célula almacena un 1 lógico, y viceversa para el 0 lógico.

Para seleccionar la fila se eleva la tensión de las dos líneas de palabra P y  $P^*$ , a 2 V y a 4,3 V, respectivamente.

Para escribir un uno se pone en baja tensión (0 V) la línea de bit izquierda. Esto, independientemente del estado anterior de  $T_1$ , polariza directamente al emisor de  $T_1$  conectado a la línea de bit izquierda. La tensión colector-emisor de  $T_1$  cae rápidamente anulando la conducción de  $T_2$ , que pasa al corte al tiempo que  $T_1$  se satura. Cuando la tensión de fila, en las líneas de palabras, vuelve a los valores de reposo, 0.3 V y 1.3 V respectivamente,  $T_1$  permanece en conducción con la corriente de base proveniente de  $R_2$ .

Para leer un 1 almacenado se selecciona la fila de idéntica forma. Los emisores conectados a la línea P quedan polarizados inversamente, y la corriente que circulaa través de  $T_1$  pasa al emisor conectado a la línea de bit izquierda. La subida resultante de tensión en la línea indica la presencia de un uno almacenado

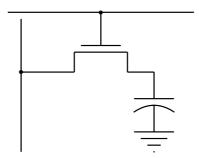

(b) Célula DRAM de un sólo transistor.

La célula DRAM de un sólo transistor consta de un transistor NMOS y un capacitor  $C_1$ , donde se guarda la información según su estado de carga.

Para seleccionar la célula, tanto para lectura como para escritura, hay que poner en conducción al transistor T a través de la línea de fila. El dato se escribe forzando la línea de columna a alto o bajo voltaje, con lo que se almacena en  $C_1$  la carga correspondiente.

En la lectura se pone en conducción a T y la capacitancia total se lee como el paralelo de  $C_1$  y  $C_2$ . Hay que restaurar el estado de carga de  $C_1$  tras cada lectura. Asímismo hay que restaurar la carga de todos los capacitores cada cierto tiempo, normalmente cada 2 ms.

Tres son las razones principales para preferir las RAM's dinámicas a las estáticas:

- 1. <u>Alta densidad</u>. Al ser más simple la celda DRAM que la SRAM pueden colocarse más celdas por chip, lo que implica un menor número de chips en el sistema.

- 2. <u>Bajo consumo de potencia</u>. La SRAM consume 0,2 mw por bit, en tanto que la DRAM consume 0,05 mw por bit, por lo que se reducen las necesidades de potencia del sistema y el coste total.

- 3. <u>Economía</u>. La DRAM es más barata por bit que la SRAM, pero necesita más circuitería de soporte y por tanto esta ventaja sólo existe en sistemas grandes de memoria.

### 1.2.

$\upliame \ \ \upliame \ \ \upliame \ \ \upliame \ \ \upliame \ \ \ \upliame \ \ \uplame \ \ \upliame \ \ \upliame \ \ \upliame \ \ \upliame \ \ \uplame \ \ \n^1\ \ \uplame \ \ \n^1\ \ \mpp$  \ \ \mpp\ \

#### Solución

Para una SRAM de 64 KB×8, como 64 KB =  $2^{16}$ , se precisan 16 líneas de direcciones  $(A_{15} - A_0)$ , y 8 líneas de datos  $(D_7 - D_0)$ , admitiendo que son bidireccionales. Para 1 MB×1, como 1 MB

$=2^{20}$ son necesarias 20 líneas de dirección, una para los datos de entrada y otra para los datos de salida.

### 1.3.

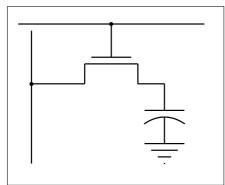

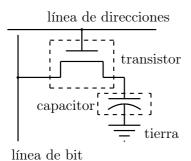

¿Qué representa la figura de la izquierda? Rotular cada una de sus partes y explicar brevemente su función.

#### Solución

La figura muestra la celda básica de almacenamiento de una memoria dinámica. La celda es capaz de guardar un bit de información, según el estado de carga del capacitor: Si el capacitor está cargado hay un 1 lógico almacenado y si el capacitor está descargado hay un 0 lógico. El transistor hace de "llave" de la carga almacenada. La línea de direcciones en alta selecciona al transistor, poniéndolo a conducir; en modo de lectura la carga se va por la línea de bit y en modo de escritura se fuerza la tensión por la línea de bit para cargar al transistor. El aislamiento del capacitor no es perfecto, descargándose poco a poco hasta perder toda la carga. Para remediar la perdida de información la celda debe "refrescarse" periódicamente.

#### 1.4.

Una cierta memoria tiene los parámetros  $t_{ACC}=300$  ns y  $t_{CR}=470$  ns (tiempos de acceso y ciclo, respectivamente). ¿Cuál es el número máximo de operaciones de lectura que pueden completarse en 1 segundo?

#### Solución

El período de lectura es el ciclo de lectura, y la frecuencia:

$$f_{Lectura} = \frac{1}{t_{CR}} = \frac{1}{470 \times 10^{-9}} = \frac{10^9}{470} = 2,128 \times 10^6$$

lecturas/segundo

Solución: 2,13 millones de lecturas.

#### 1.5.

¿Qué se entiende por Módulo DIMM DDR SDRAM?

### Solución

DIMM son las siglas de «Dual In-line Memory Module» y que podemos traducir como Módulo de Memoria lineal doble. DDR, del acrónimo inglés Double Data Rate, significa memoria de doble tasa de transferencia de datos en castellano. SDRAM (del inglés, Synchronous Dynamic Random Access Memory, es decir, memoria RAM dinámica de acceso síncrono).

#### 1.6.

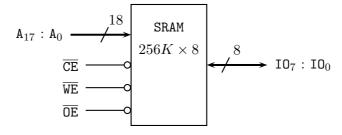

Se dispone de memoria del tipo CY7C1010DV33 (256K×8) cuyo diagrama de bloque se muestra a continuación.

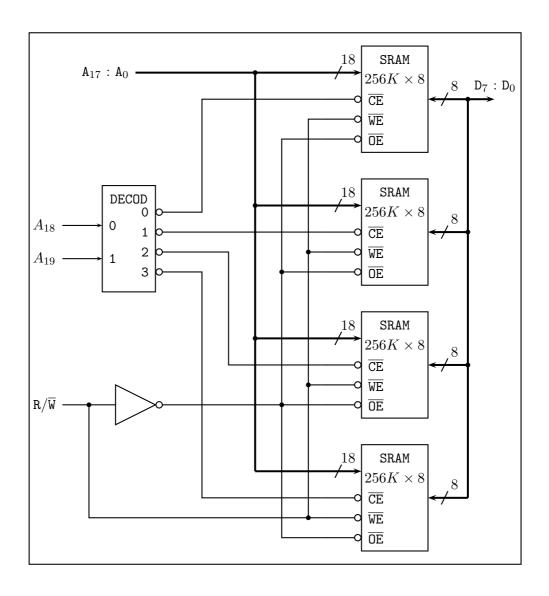

Si el procesador al que se debe conectar posee 20 líneas para generar las direcciones y una línea de lectura/escritura  $(R/\overline{W})$ . Se pide

- a) Diseñar el mapa de memoria, mediante decodificadores para direccionar  $512 \text{K} \times 32$ , cuya primera dirección sea 00000h.

- b) Diseñar el mapa de memoria, mediante decodificadores para direccionar 1M×8, cuya primera dirección sea 00000h.

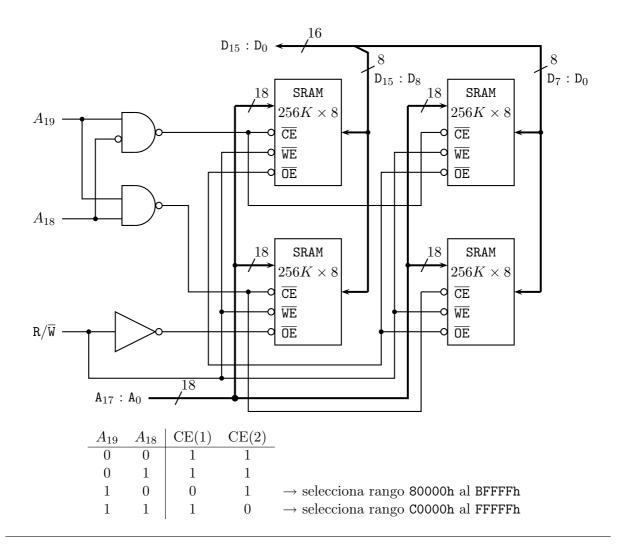

- c) Diseñar el mapa de memoria, mediante decodificadores para direccionar 512K $\times$ 16, cuya primera dirección sea 80000h.

#### Solución **Solución**

(a)

|       |               | A | 19 | $A_{18}$ |

|-------|---------------|---|----|----------|

| 00000 |               |   |    |          |

|       | $256K\times8$ | ( | )  | 0        |

| 3FFFF |               |   |    |          |

| 40000 |               |   |    |          |

|       | $256K\times8$ | ( | )  | 1        |

| 7FFFF |               |   |    |          |

| 80000 |               |   |    |          |

|       | $256K\times8$ | 1 |    | 0        |

| BFFFF |               |   |    |          |

| C0000 |               | _ |    |          |

|       | $256K\times8$ | 1 | _  | 1        |

| FFFFF |               |   |    |          |

Los cuatro bloques de  $256K \times 8$  hacen el  $1M \times 8$ .

Se decodifican las líneas  $A_{18}$  y  $A_{19}$  y hacen falta 4 chips.

(b)

|        |         |   | $A_{19}$ | $A_{18}$ |           |

|--------|---------|---|----------|----------|-----------|

| 00000h |         |   |          |          |           |

|        | vacía   |   | 0        | ×        |           |

|        |         |   |          |          |           |

| 80000h |         | - |          |          |           |

|        |         |   |          | 0        | } 256K×16 |

|        |         |   | _        | 0        | f 256K×16 |

|        | 512K×16 |   | 1        |          |           |

|        |         |   |          | 1        | 256K×16   |

| FFFFFh |         |   |          |          | ,         |

|        | I       | l |          |          |           |

### 1.7.

- a) ¿Cuántos chips de RAM de 32K×8 se necesitan para tener una capacidad de memoria de 256Kbytes?

- b) ¿Cuántas líneas de dirección se necesitan para acceder a 256Kbytes?¿Cuántas de esas líneas están conectadas a las entradas de dirección de todos los chips?

- c) ¿Cuántas líneas deben decodificarse para las entradas de selección de chip? Especificar el tamaño del decodificador.

#### Solución

(a) Los chips de  $32K \times 8$  tienen un ancho de palabra de un byte. Así pues,

$$\frac{256K}{32K} = \frac{2^{18}}{2^{15}} = 2^3 = 8 \text{ chips.}$$

(b)  $256K = 2^{18} \Longrightarrow 18$  líneas de dirección. A cada chip entran 15 líneas, pues  $2^{15} = 32K$ .

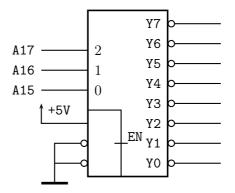

c) 18 - 15 = 3 líneas deben decodificarse.

Lo más fácil es usar un decodificador de 3-a-8 como, por ejemplo, el conocido 74138:

## 1.8.

Un computador tiene 1 Mbyte de capacidad de direccionamiento. ¿Cuántos chips de 16 Knibbles se pueden conectar como máximo al sistema?

## Solución

1 Mbyte  $\div$  16 Knibbles =  $(2^{20} \times 2) \div (2^{14} \times 1) = 2^6 \times 2 = 128$  chips.